위성 탑재 영상레이다의 온보드 데이터 압축을 위한 비정수배 데시메이션 필터 최적화 설계 기법

Optimization Design of Non-Integer Decimation Filter for Compressing Satellite Synthetic Aperture Radar On-board Data

Article information

Abstract

Abstract

The on-board processor of satellite Synthetic Aperture Radar(SAR) digitizes the back-scattered echoes and transmits them to the ground. As satellite SAR image of various operating conditions including broadband and high resolution is required, an enormous amount of SAR data is generated. Decimation filter is used for data compression to improve the transmission efficiency of these data. Decimation filter is implemented with the FIR(Finite Impulse Response) filter and here, the decimation ratio and tap length are constrained by resource requirements of FPGA used for implementation. This paper suggests to use a non-integer ratio decimation filter in order to optimize the data transmission efficiency. Also, it proposes a filter design method that remarkably reduces the resource constraints of the FPGA in-use via applying a polyphase filter structure. The required resources for implementing the proposed filter is analysed in this paper.

1. 서 론

위성 탑재 영상레이다는 임무 수행을 위해 안테나에서 첩 신호를 방사하고 목표물에 후방 산란되어 들어오는 신호를 수신한다[1]. 수신 데이터는 디지털 신호처리를 통해 가공되어 지상으로 전송되고, 지상에서는 수신 받은 데이터를 처리하여 영상으로 복원한다. 이때, 위성 탑재 영상레이다는 지상으로 데이터를 전송하는 과정에서 데이터 전송 효율을 높이기 위해 데이터 압축 처리가 요구된다[2]. 데이터 압축은 크게 데이터의 샘플 수에 대한 압축과 데이터의 양자화 비트수에 대한 압축으로 나누어진다. 이 중, 데이터의 샘플 수에 대한 압축은 구현의 복잡성을 해소하기 위해 주로 유한 임펄스 응답 필터를 이용한 데시메이션이 수행된다[3]. 일반적으로 위성 탑재 영상레이다에 사용되는 데시메이션 필터는 기존에 연구된 정수배의 데시메이션 비율을 갖는 필터[4]를 2단 직렬형으로 구성하여 사용한다. 이는 두 개의 데시메이션 비율의 조합으로 다양한 데시메이션 비율을 구현할 수 있는 장점이 있다. 하지만 정수배 데시메이션 비율로 인해 데이터 량을 최적화 하지 못하는 큰 한계가 있다. 예를 들어 데시메이션 비율 2:1과 1.5:1은 전송해야 되는 데이터 량에 큰 차이가 존재한다. 신호의 대역폭이 0.6π인 신호에 데시메이션 비율 2:1 적용은 엘리어징 발생(0.6*2>1)으로 적용이 어렵다. 하지만 데시메이션 비율 1.5:1은 엘리어징 미발생(0.6*1.5<1)으로 적용이 가능하다. 따라서 정수배 데시메이션 비율로는 데이터 량을 감소시키는 것이 불가능하며 데이터량은 1.5배의 차이가 있게 된다.

위성 탑재 영상레이다의 시스템 요구 성능에 의해 데시메이션 비율, 유한 임펄스 응답 필터의 리플, 감쇠, 천이 대역폭과 같은 데시메이션 필터 규격이 도출된다. 이와 같은 규격들은 유한 임펄스 응답 필터가 필요로 하는 계수의 차수와 연관된다[5]. 요구되는 필터 계수의 차수는 구현 측면에서 FPGA(Field Programmable Gate Array)의 리소스 소요량과 직접적인 관계가 있다.

또한, 위성 탑재 영상레이다에서 사용되는 FPGA는 우주환경의 영향을 고려하여 TMR(Triple Module Redundancy)구조 및 권장 클락 주파수 등에 대한 제한이 있기 때문에 사용 가능한 리소스에는 더욱 강한 제약이 발생한다[6]. 이와 같은 이유로 위성 탑재 영상레이다에서 사용할 유한 임펄스 응답 필터를 설계할 때, 리소스 소요량을 최소화하는 방법이 함께 고려되어야 한다.

본 논문에서 제안하는 방식은 기존의 영상레이다 분야에서 연구된 정수배 데시메이션 비율을 갖는 필터들의 조합과 달리 비정수배의 데시메이션 비율을 갖는 필터와 정수배의 데시메이션 비율을 갖는 필터를 조합한다. 이는 우주 환경에서 동작 주파수에 대한 부담과 FPGA 리소스 소요량에 대한 부담으로 업 샘플링 구현에 대한 기피를 제안한 방법을 통해 업 샘플링 구현에 대한 부담을 극복하여 업 샘플링과 다운 샘플링의 조합으로 비정수배 비율의 데시메이션 필터를 구현하여 다양한 데시메이션 비율을 제공함과 동시에, 시스템에서 요구하는 데시메이션 비율로 데이터 량을 최적화 하는 큰 장점이 있다. 또한, 유한 임펄스 응답 필터를 구현함에 있어서 폴리페이즈 구조의 로직 설계를 적용하여 FPGA의 리소스 소요량에 대한 부담을 감소시키는 필터 최적화 설계 방법에 대해 제시한다. 제안하는 방식의 검증을 위해 성능 분석을 수행하고 보드 레벨 구현 가능성 검증을 위해 리소스 분석을 수행하였다.

2. 비정수배 데시메이션 필터 구조

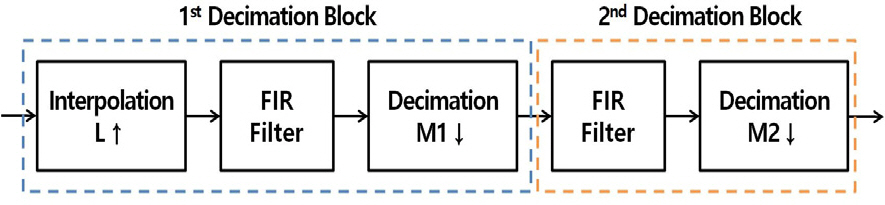

Fig. 1은 본 논문에서 제시하는 2단 직렬형 구조의 비정수배 데시메이션 필터를 나타낸다. 그림에서 첫 번째 데시메이션 블록은 비정수배의 데시메이션 비율을 구현하기 위해 유한 임펄스 응답 필터 전단에 인터폴레이션이 수행되고, 유한 임펄스 응답 필터 후단에 데시메이션이 수행된다. 첫 번째 블록에서의 데시메이션 비율은 M1/L로 나타난다.

두 번째 데시메이션 블록은 정수배의 데시메이션 비율이 구현되며 유한 임펄스 응답 필터 후단에서 데시메이션이 수행된다. 2단 직렬형 구조의 최종 데시메이션 비율은 M1*M2/L로 나타난다. 비정수배가 고려되지 않는 경우, 2단 직렬형 구조의 데시메이션 비율은 M1*M2로 나타날 것이며 M1과 M2의 값이 1,2,3,4.로 증가되는 정수 값을 대입하여 조합하면 값이 커질수록 최종 데시메이션 비율 간의 간격이 매우 커짐을 확인할 수 있다. 반면에 비정수배의 데시메이션 비율이 고려되는 경우, L의 존재로 인해 최종 데시메이션 비율 간의 간격은 좁아지고 보다 미세한 조정이 가능하여 데이터 량의 최적화에 유리하게 된다.

3. 필터 설계 방법

본 논문에서는 폴리페이즈 구조를 통해 비정수배의 데시메이션 비율을 갖는 유한 임펄스 응답 필터와 정수배의 데시메이션 비율을 갖는 유한 임펄스 응답 필터의 조합으로 필터를 설계하는 방법을 제시한다. 먼저, 비정수배의 데시메이션 비율을 갖는 유한 임펄스 응답 필터를 1단 필터라고 칭하고 정수배의 데시메이션 비율을 갖는 유한 임펄스 응답 필터를 2단 필터라고 칭한다.

3.1 폴리페이즈 필터 구조

폴리페이즈 구조를 적용함으로써 업-샘플링과 다운-샘플링 수행에 있어서 불필요한 연산에 해당하는 필터 계수를 제외하고 필터 계수를 그룹화 하여 연산에 적용할 수 있다[7]. 업-샘플링을 수행한 후, 일반적인 유한 임펄스 응답 필터 연산의 입력으로 업-샘플링되어 삽입되는 0에 대한 불필요한 연산을 제외하면, 출력 연산에 관여하는 필터 계수는 업-샘플링 비율에 따라 동일한 간격을 갖는 것을 확인할 수 있고, 동일한 간격을 갖는 필터 계수끼리 그룹화 시킬 수 있다. 이에 따라, 1단 필터에 폴리페이즈 구조를 적용하여 연산이 수행되는 시점에 필터 계수 그룹을 변화시키면 FPGA가 사용하는 리소스 소요량이 감소하여 필터 연산을 수행할 수 있다. 1단 필터의 폴리페이즈 구조의 원리에 대한 이해를 위해 업-샘플링 비율 L이 2인 경우를 예를 들어 설명한다.

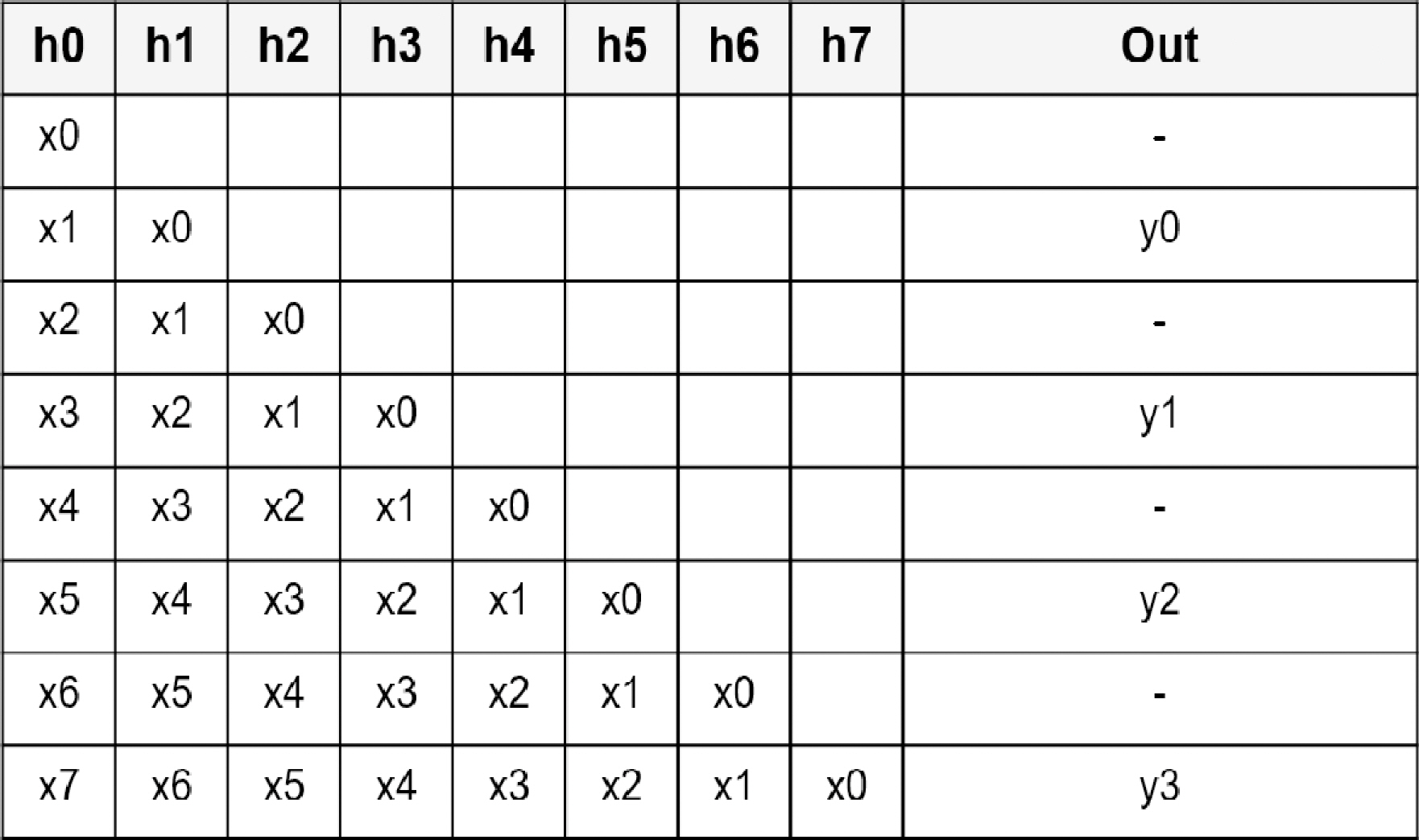

Fig. 2는 2배의 업-샘플링이 수행되는 유한 임펄스 응답 필터의 연산을 나타낸다. 1단 필터의 폴리페이즈 구조는 업-샘플링 비율 2에 따라서 필터 계수들을 2개로 그룹화 시킬 수 있다. 필터 계수를 2개의 그룹으로 분리하므로 필터 계수의 차수가 2배 감소하며 이는 FPGA의 리소스 소요량이 절반으로 감소함을 의미한다.

다음으로, 폴리페이즈 구조에서 다운-샘플링의 원리에 대한 이해를 위해 2단 필터에서 다운-샘플링 비율 M이 2인 경우를 예를 들어 설명한다. Fig. 3은 다운-샘플링이 수행되는 유한 임펄스 응답 필터의 연산을 나타낸다.

다운-샘플링을 수행할 때, 필요로 하는 출력만을 보면 2개의 그룹화된 계수에 대한 연산에 해당하는 항이 출력마다 더해지는 것을 확인할 수 있다. 이때, 필터 계수와 연산을 이루는 입력이 다운-샘플링 비율에 따라 동일한 간격을 갖는 것을 확인할 수 있다. 이는 입력이 M번 쉬프트 되는 동안 M개의 필터 계수 그룹을 순서대로 곱하고 더해 출력하면 원하는 출력을 얻을 수 있다는 것을 의미한다. 이와 같은 원리로 2단 필터의 폴리페이즈 구조를 적용한다.

결과적으로 2단 필터의 폴리페이즈 구조는 다운-샘플링 비율 2에 따라서 필터 계수들을 2개로 그룹화 할 수 있고, 1단 필터의 경우와 마찬가지로 FPGA의 리소스 소요량을 절반으로 감소시킨다.

3.2 폴리페이즈 구조 구현 방안

본 논문에서 제안하는 방법을 FPGA에서 구현하기 위해서는 불필요한 연산을 수행하지 않는 동작의 구현이 우선시되어야 하고, 필터 계수 그룹의 스위칭 동작이 함께 구현되어야 한다.

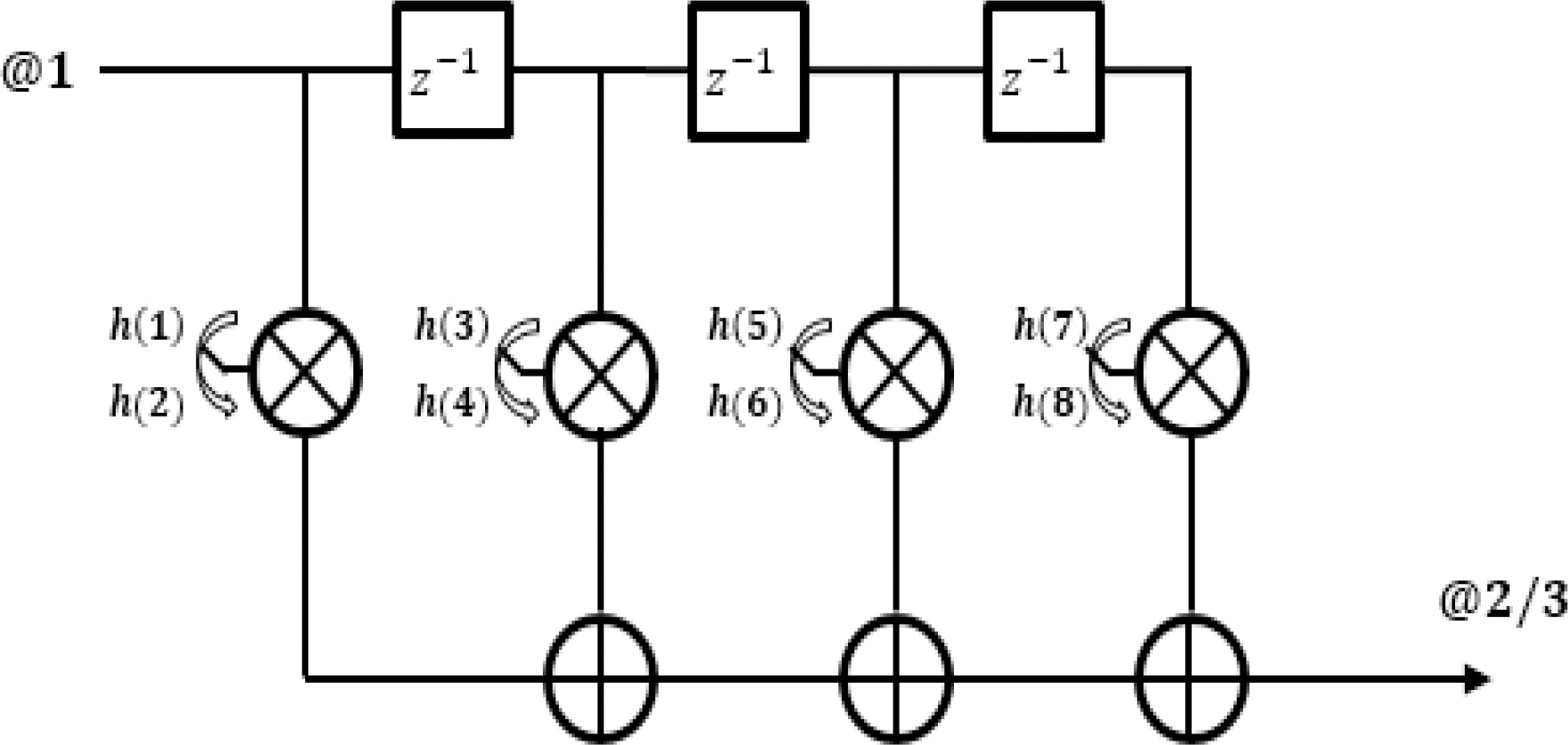

Fig. 4는 Fig. 2의 예시에 대해 제안하는 방법의 로직 구조를 나타낸다. 필터의 필요한 차수가 8이라면 업-샘플링 비율이 2이므로 제안하는 방법을 통해 차수는 4로 감소한다. 이 구조에서 유한 임펄스 응답 필터의 출력 동작 주파수는 입력을 기준으로 입력 클락 주파수가 1이라고 할 때, 업-샘플링과 다운-샘플링의 비율에 따라 L/M으로 정의되고 L/M 주파수에 따른 필터 계수 그룹의 스위칭 동작은 정류자에 의해 구현된다. 예를 들어, L과 M이 각각 2와 3이면 출력 동작 주파수는 Fig. 4와 같이 2/3의 주파수로 동작하게 되며 필터 계수 그룹은 2/3의 주파수로 스위칭 되어 동작한다.

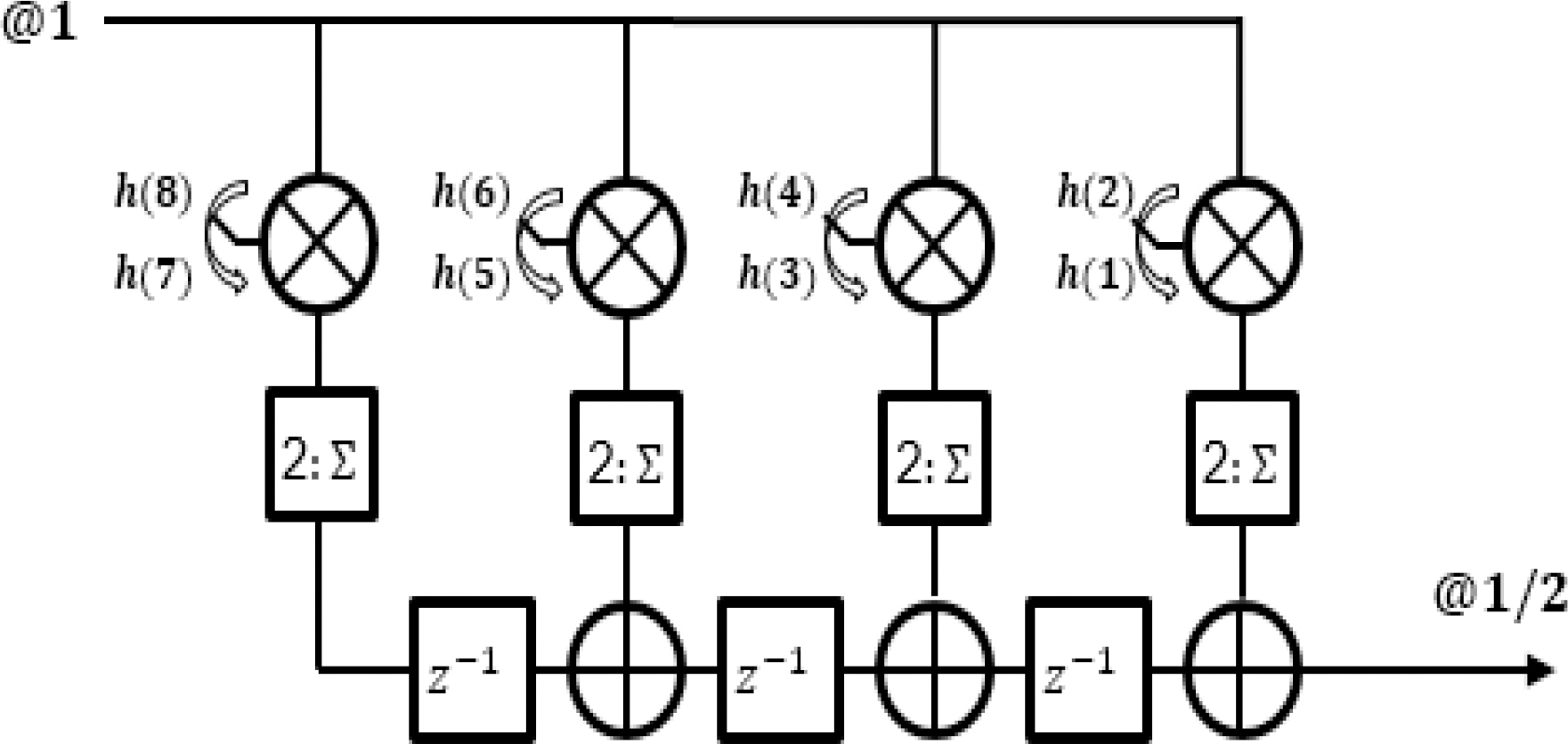

Fig. 5는 Fig. 3의 예시에 대해 제안하는 방법의 로직 구조를 나타낸다. 필터의 필요한 차수가 8이라면 다운-샘플링 비율이 2이므로 제안하는 방법을 통해 차수는 4로 감소한다. 유한 임펄스 응답 필터의 출력 동작 주파수는 입력을 기준으로 입력 클락 주파수가 1이라고 할 때, 다운-샘플링의 비율에 따라 1/M으로 정의된다. 로직 구조에서 필터 계수 그룹의 스위칭 주파수는 입력과 동일하게 1로 동작하나 곱셈 연산이 M만큼 누적되어 더해져 출력되기 때문에 출력 주파수는 1/M으로 동작하게 된다. M이 2인 예를 고려할 때 출력 동작 주파수는 Fig. 5와 같이 1/2의 주파수로 출력하게 되며 필터 계수 그룹은 1의 주파수로 스위칭 되어 동작한다.

4. 제안한 방법의 성능 및 리소스 분석

제안한 방법으로 설계된 필터의 분석을 수행하기 위해 영상레이다의 첩 신호의 파라미터를 가정하고 이상적인 첩 신호에 제안한 방법으로 설계된 필터를 적용하여 데시메이션을 수행한다. 성능 검증을 위해 영상레이다의 성능 지표로 활용되는 IRF(Impulse Response Function) 특성을 비교하고 리소스 분석을 위해 우주 급에 사용되는 FPGA의 리소스와 제안한 방법의 FPGA 리소스 소요량을 비교하여 보드 레벨 구현 가능성을 검증한다.

4.1 IRF 분석 기법

영상레이다는 획득하고자 하는 영상이 요구하는 해상도에 따라 필요로 하는 첩 신호의 대역폭을 계산한다. 계산된 값에 따라 이상적으로 설계된 첩 신호의 IRF 특성은 데이터 압축을 위해 수행되는 디지털 신호처리 과정을 거치면서 진폭 왜곡이 더해지고, 데이터 압축에 의한 위상 오차 성분이 더해져 저하되어 나타난다.

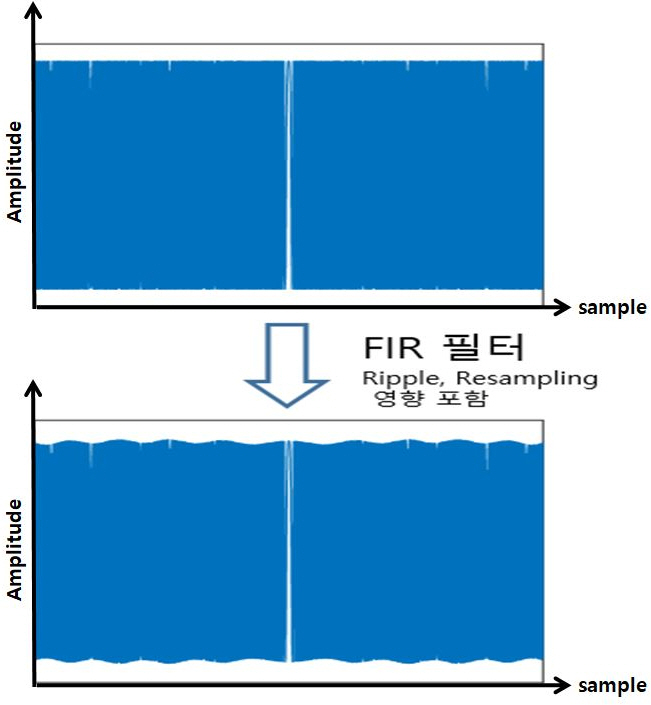

Fig. 6은 데이터 압축을 위한 디지털 필터링 과정에서 리플 등의 진폭 왜곡이 더해지는 것을 직관적으로 나타낸다. 아날로그와 다르게 디지털 영역은 비연속적이기 때문에 필터 응답에 리플과 같은 왜곡이 나타나게 된다.

본 논문에서는 제안한 방법으로 설계된 필터의 성능을 분석하기 위해 이상적인 첩 신호와 일반적인 콘볼루션 필터 출력간의 IRF 특성 그리고 이상적인 첩 신호와 제안된 방법으로 설계된 필터 출력과의 IRF 특성을 비교 분석 한다.

4.2 IRF 성능 분석결과

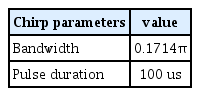

성능 분석을 위해 사용되는 첩 신호의 파라미터는 Table 1과 같다. 선정된 첩 신호의 파라미터는 데시메이션 적용 후, 샘플링 주파수 기준 약 15 %의 오버샘플링 여유를 갖는 대역폭과 1 PRI가 1 kHz인 경우 첩 신호의 duty가 10 %인 신호 길이를 선정하였다. 이는 데시메이션 후의 엘리어징 영향성이 고려된다.

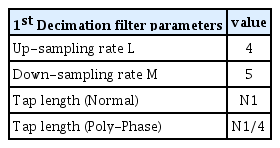

성능 분석을 위해 사용되는 1단 필터의 파라미터는 Table 2와 같다.

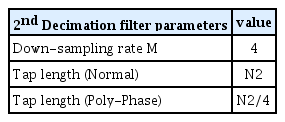

성능 분석을 위해 사용되는 2단 필터의 파라미터는 Table 3과 같다.

다음은 제안한 필터의 성능 검증을 위해 수행한 IRF분석 결과이다. IRF 성능은 1단과 2단에서 각각이상적인 첩 신호와 일반적인 콘볼루션 필터 출력 신호간의 IRF, 이상적인 첩 신호와 폴리페이즈 구조의 필터 출력 신호간의 IRF의 비교로 수행된다.

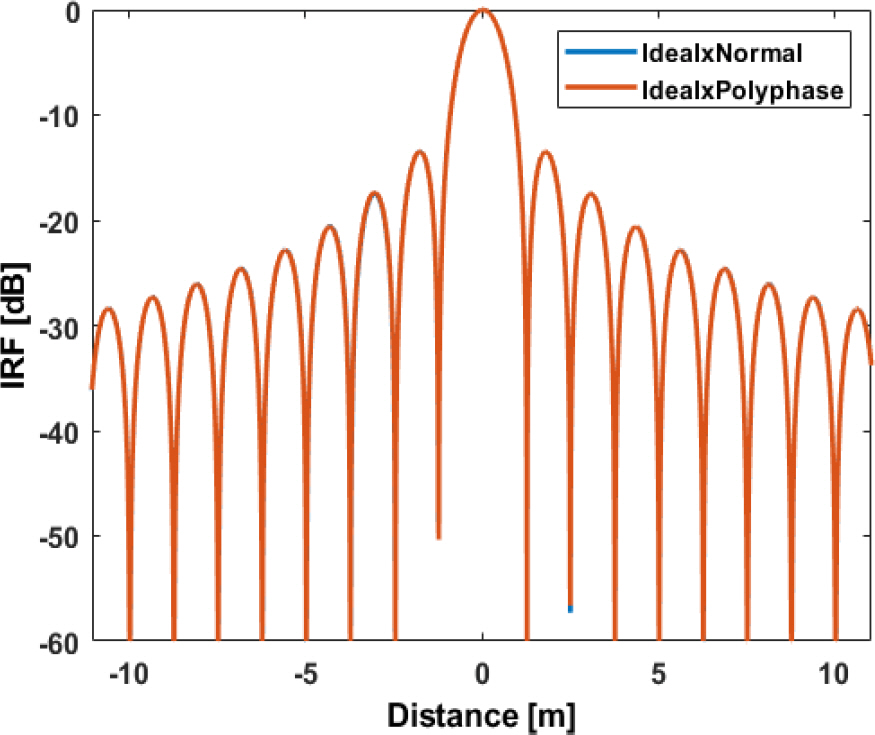

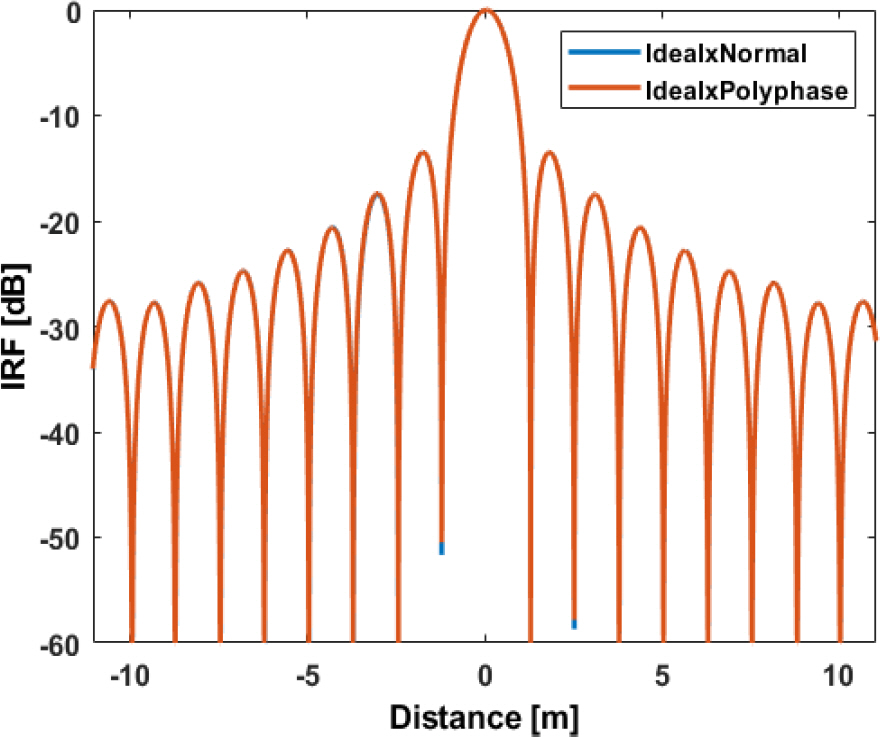

Fig. 7은 1단 필터에서의 IRF를 나타내고, Fig. 8은 2단 필터에서의 IRF를 나타낸다.

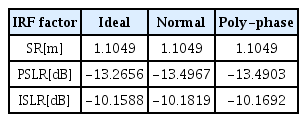

Table 4는 1단 필터에서의 IRF 성능지표 비교를 나타내고, Table 5는 2단 필터에서의 IRF 성능지표 비교를 나타낸다.

IRF 성능분석 결과에서 제안한 필터 설계 방법은 1단 필터에서 일반적인 콘볼루션 필터 대비 SR: 0 m, PSLR: 0.0091 dB, ISLR: 0.0134 dB 차이를 보였으며 2단 필터에서 일반적인 콘볼루션 필터 대비 SR: 0 m, PSLR: 0.0064 dB, ISLR: 0.0191 dB 차이를 보였으며 제안한 방법으로 설계된 필터의 출력들이 일반적인 콘볼루션 필터 출력과 동일한 해상도를 갖는 것을 확인할 수 있다.

4.3 리소스 분석

FPGA의 리소스를 사용하여 제공할 수 있는 Multiplier 수는 FPGA로 구현하고자 하는 필터가 갖는 계수의 차수와 연관성이 있다.

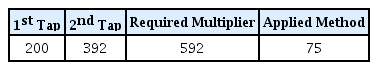

다음은 본 논문에서 설계한 일반적인 콘볼루션 필터가 갖는 최대 계수의 차수를 기반으로 구현에 필요한 Multiplier의 필요량과 제안한 방법을 적용할 때 구현에 필요한 Multiplier의 필요량을 나타낸다.

Table 6에서 제안한 방법을 적용한 경우의 Multiplier 필요량은 1단 필터에 업 샘플링 4, 2단 필터의 최대 다운 샘플링 16인 경우를 가정하며 폴리페이즈 구조에 의해 200/4 + 392/16로 계산될 수 있다.

필터가 갖는 최대 계수의 차수를 기반으로 FPGA에서 Multiplier를 592개 이상이 제공되어야 보드 레벨 구현이 가능하지만 제안한 방법을 적용하면 Multiplier 재사용으로 인해 75개 이상 제공이 가능하면 온보드 구현이 가능해진다.

위성에서 사용되는 Microcemi 사의 우주급 FPGA모델인 RTG4와 Xilinx 사의 우주급 FPGA모델인 Virtex5의 경우, TMR구조를 반영할 때 320∼462개의 가용한 Multiplier 수를 제시하고 있다. 이를 Table 6과 비교해보면 제안한 필터 구조를 적용함으로써 우주급 FPGA 에 구현이 가능함을 확인할 수 있다.

실제로 보드 레벨 구현을 위해 사용하고자하는 클락 주파수 및 영상레이다가 요구하는 첩 신호의 대역폭의 영향에 따라 병렬구조화가 필요로 하는 경우도 존재한다. 하지만 병렬구조화를 고려하더라도 제시한 방법에 의한 리소스 저감 효과는 분명하다.

5. 결 론

본 논문에서는 위성 탑재 영상레이다의 데이터 전송 효율성을 증대하기 위한 데이터 압축에 필요한 데시메이션 필터 설계 방법과 성능에 대해 기술하였다. 폴리페이즈 구조를 이용하여 FPGA 리소스 소요량을 감소시킬 수 있는 데시메이션 필터 설계 방법을 제시하였으며, 필터 계수를 그룹화하고 데시메이션 비율에 따라 연산에 관여되는 필터 계수 그룹을 스위칭하는 동작 구현 방안을 확인하였다.

제안한 방법으로 설계된 데시메이션 필터와 일반적인 콘볼루션 방식의 데시메이션 필터의 출력 신호를 이용하여 동일한 해상도의 IRF특성을 갖는 신호를 얻을 수 있음을 확인하였다. 또한 제안한 방법의 필터 구조를 구현함에 있어 필요한 FPGA Multiplier 수와 우주급 FPGA의 사양을 비교하여 보드 레벨 구현의 가능성과 제안한 방법의 리소스 저감 효과를 확인하였다.

본 논문에서 제안한 위성 탑재 영상레이다의 온보드 데이터 압축을 위한 비정수배 데시메이션 필터 최적화 설계 방법은 위성 탑재 영상레이다의 데이터 압축에 필요한 데시메이션 필터의 보드 레벨 구현에 대한 FPGA 리소스 소요량 부담을 개선하고 가용한 데시메이션 비율의 효율성을 증대하는 방향으로 활용할 계획이다.