VST 및 FPGA를 이용한 전자표적 생성 및 신호 모의장치 개발

The Development of the Real Time Target Simulator for the RF Signal of Electronic Warfare using VST and FPGA

Article information

Trans Abstract

In this paper, the target simulator for RF signals was developed by using VST(Vector Signal Transceiver) and set by real-time signal processing SW programs. A function to process RF signals using FPGA(Field Programmable Gate Array) board was designed. The system functions capable of data processing, raw signals monitoring, target signals(simulated range, velocity) generating and RF environments data analyzing were implemented. And the characteristics of modulated signal were analyzed in RF environment. All function of programs for processing RF signal have options to store signal data and to manage the data. The validity of the signal simulation was confirmed through verification of simulated signal results.

1. 서 론

현대화된 전장에서 아군의 생존 확률을 극대화 시키기 위해 다양한 군사 기술들이 개발되어왔다. 특히 전자전 분야는 전자기적 스펙트럼을 역으로 이용하여 적을 무력화시킬 수 있어 아군의 전력을 효율적으로 보호할 수 있다. 전자기 에너지를 사용하는 군사적 활동을 통해 적군의 감시정찰 체계를 무력화 및 파괴하고 전자기적인 간섭으로부터 아군의 전투 체계 운용을 안정적으로 보장할 수 있는 것이다[1,2]. 이라크전 및 걸프전에서도 지휘통제망을 마비시켜 그 중요성이 입증된 바 있으며, 현대전에서 전자전 기술은 매우 중요한 핵심기술이라고 볼 수 있다. 전자전 전투기법은 공격 방법에 따라서 다양한 방식으로 나눌 수 있다. 그 방식은 전자지원책(ESM), 전자방해책(ECM), 전자방해방어책(ECCM) 이다. 특히 전자방해책(ECM)은 채프(Chaff), RAS(Radar Absorbing Structure), RAM(Radar Absorbing Material)를 이용하는 수동형 방식과 전파 방해를 이용한 능동형 방식으로 나뉠 수 있다. 반사체 및 전파 흡수체 등을 이용하는 수동형 방식과 달리, 능동형 전자 방해책은 전파를 송신하여 기만하는 것이 핵심이며, 크게 잡음 방해와 기만 방해로 분류한다. 첫 번째로 잡음 방해의 경우 표적의 위치를 나타내는 신호를 강력한 방해 전파를 적의 레이다에 방사하여 자신의 위치를 오인시키는 방식이다. 두 번째로 기만 방해의 경우 적의 레이다에 변조된 신호를 방사하여 반사된 표적의 위치를 변조시키는 방식이다[3]. 이러한 전자전 기법과 방법론을 기반으로 재밍(Jamming)과 관련된 다양한 기술들이 계속해서 발전되고 있다.

다양한 펄스 신호에서 변조 기법을 적용할 수 있는 레이다가 등장하였고, 레이다 신호를 세부적으로 식별/변조하기 위한 기술이 발맞추어 개발되었다. 변조 기술이 고도화되면서 레이다 신호를 식별하는 것에 대해서 높은 해석 능력을 요구하게 되었다[4]. 하드웨어를 기반으로 설계된 장치를 이용하여 모노 펄스 레이다에서 방사한 RF 신호를 추출하여 위협 시스템의 위치에 대한 정보를 역 추적하는 기법들이 개발되었으며, 적 레이다를 교란 및 기만하여 아군의 위치 정보가 노출되는 것을 방지하기 위한 다양한 재밍 기법들도 개발되었다[5]. 특히 전자전 무기체계에서는 다양한 레이다를 바탕으로 신호를 실시간으로 재밍하는 능력이 적을 교란하기 위해 매우 중요하다. 따라서 실시간 재밍기법을 발전시키는 방향으로 다양한 연구가 진행되었다. 이에 신호 파형을 실시간으로 주파수와 시간 정보를 변경하여 동시에 다수의 레이다를 재밍 할 수 있는 알고리즘과 기법도 연구된 바 있다[6].

또한 레이다에서 발생한 RF 원 신호의 샘플링 방식에서 기존 DRFM(Digital Radio Frequency Memory) 시스템 구조를 사용시에 위상의 불연속점이 발생하는 문제를 해결하기 위해서, 기존 구조에서 더 나아가 진폭 샘플링 방식의 Recirculation을 사용하여 크기 반전 보전 기법을 적용한 진폭 샘플링 방식의 DRFM 구조 및 기술이 연구되었다[7]. 레이다 신호 형태뿐 아니라 SAR 위성 신호에 대해서도 재밍 하는 기법이 연구되었는데, SAR 영상 신호에 대해서 Chirp 신호를 함께 시간 동기화시켜 재밍을 하게되면 그 효과가 극대화 될 수 있다는 연구 결과가 보고된 바 있다[8]. 이처럼 다양한 환경에서 여러 신호들을 바탕으로 재밍과 관련된 시뮬레이션을 진행 되었으며, 이와 관련된 기법에 대해 이론적으로 서술되었지만 신호 수신기 및 처리기를 이용해 실시간 재밍장치를 개발한 연구는 아직 많지 않다.

본 논문에서는 VST(Vector Signal Transceiver)를 이용하여 신호 입력장치로부터 수신된 RF 신호를 처리 및 모의할 수 있는 장치를 개발하였다. 설계된 장치를 통해 재생/저장, 신호 모의, 전파 환경 계측 기능을 구현하였다. 개발된 VST 모듈 내 탑재된 FPGA 보드를 이용해 고속화된 샘플링 기능을 통해 입력된 신호를 처리 하였으며, 실시간 데이터 처리가 가능하도록 설계하였다. 또한 신호 데이터를 처리하기 위해 NI(National Instrument) 사의 LabVIEW를 통해 소프트웨어를 구현하였다.

논문의 구성은 다음과 같다. 먼저 2장에서는 개발된 VST 장비의 기본 시스템 구조와 상세한 스펙에 대해 서술한다. 이때 VST를 통한 신호 모의 핵심 개념을 함께 서술한다. 3장에서는 구현된 LabVIEW 소프트웨어의 알고리즘과 설계 내용을 서술하였다. 마지막으로 4장에서는 각 소프트웨어 기능에서 진행된 시뮬레이션 결과와 분석내용을 서술하였다. 논문에서 개발된 소프트웨어는 크게 3가지의 기능으로 설계되었다. 첫 번째 RF 레코더는 입력된 설정 값을 바탕으로 신호를 모니터링 하고, 신호를 저장하고 재생할 수 있는 기능을 구현하였다. 파일 관리 기능을 통해 저장된 파일을 재생하여 현재 파일과 비교분석이 가능하다. 두 번째로 전자표적처리 소프트웨어를 구현하였다. 입력된 RF 신호에 대해 거리 및 속도 모의가 가능하도록 구현하였으며, 신호 모의 알고리즘과 시뮬레이션 결과를 분석 및 검증하였다. 세 번째로 전파환경 소프트웨어에서는 전파환경에 대한 신호 특성을 분석하는 기능을 구현하여 입력된 신호를 측정하여 결과를 확인하였다. 각 소프트웨어 기능에서 구현된 핵심 원리를 먼저 순서대로 설명하고, 시뮬레이션 진행 후 도출되는 결과와 측정 데이터의 타당성 확인 하는 순서로 서술하였다.

2. VST 시스템 구성 및 원리

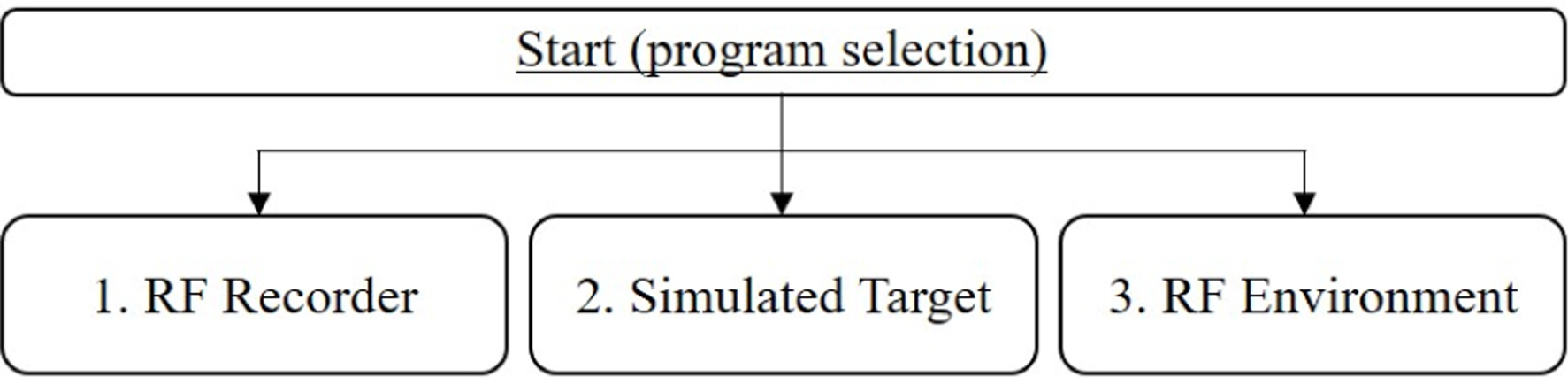

본 논문에서 개발된 VST 장비는 다양한 무기체계 중 유도무기와 비행체 개발 및 시험평가에 적용하기 위해 설계되었다. 장비를 통해 표적의 반사 신호를 직접 계측하고 신호처리 할 수 있고, 타 레이다의 수신 신호를 외부 입력하여 신호모의가 가능하도록 설계되었다. 운용자가 장비에서 직접 저장, 분석, 시간지연, 도플러 신호를 모의 및 재생할 수 있는 소프트웨어 기능을 구현하였다. 또한 시험을 진행하는 구역에서 원격측정 및 레이다 주파수 대역에 대한 전파환경 신호 모니터링이 가능하도록 구현하였다. 시스템을 제어하기 위해 NI사의 LabVIEW를 기반으로 하여 소프트웨어를 설계하였다. SW는 총 3개로 분리되어 설계되었는데 첫 번째로, RF 신호를 계측하고 저장할 수 있는 기능을 담당하는 RF Recoder SW, 두 번째로 가상의 표적을 생성하여 거리 및 속도를 모의시키는 Simulated Target SW, 마지막으로 변조된 신호의 전파환경 신호를 계측 할 수 있는 RF Environment SW 로 구성된다. 각 SW는 개별적으로 사용되며, 초기 프로그램 진입 시 3가지 중 하나를 선택하여 실행된다. Fig. 1에 선택 가능한 프로그램 구성을 나타내었다.

2.1 VST 플랫폼 구성 및 개념도

Fig. 2는 VST의 기본 구조를 나타낸다. 그림과 같이 하드웨어를 패키지화하는 섀시(PXIe-1085)와 각 모듈은 유기적으로 기능을 수행한다. Windows OS 및 소프트웨어 컨트롤러를 담당하는 PXIe-8880, 신호의 전반적인 처리를 담당하는 PXIe-5840, Xilinx vivado에 확장가능한 소프트웨어를 사용하는 PXIe-7915, 신호 데이터의 저장소 역할을 하는 DM4M.2 모듈과 GPS 및 Clock 동기화를 담당하는 PXIe-6674T와 PXI-6683T 로 구성된다. PXIe-5840, PXIe-7915, DM4.M은 2개 쌍으로 구성되어 총 10개의 모듈이 섀시에 연결되는 형태로 시스템이 구성되었다.

Table 1은 VST에서 구성되는 모듈의 하드웨어의 스펙을 나타낸다. 시스템에서 최초 입력된 RF 신호를 Digital로 변환하는 ADC(Analog to Digital Converter)의 경우 16 bit의 해상도를 가지고 있으며 1.25 GHz의 Sample rate와 1.25 GS/s의 I/Q Data Rate를 가지고 있다. DAC(Digital to Analog Converter)의 경우 마찬가지로 해상도는 16 bit로 설정되었다. VST 내부에는 LabVIEW 자체 툴을 통해 FPGA 컴파일이 수행될 수 있고, Xilinx 컴파일 툴이 설치되어 컴파일 시간을 단축시키고 수정할 수 있도록 구현하였다. 특히 보드에 탑재된 FPGA를 활용하면 고속 데이터 처리가 가능한 로직을 설계 할 수 있는데, LabVIEW 내 FPGA 모듈을 이용하면 구현이 가능 하다. 모듈을 통해 신호의 특정 부분을 필터링 할 수 있고 원하는 데이터 값으로 신호 모의가 가능하다. 본 논문에서 설계된 소프트웨어에서 LabVIEW FPGA 시퀀스 모듈을 사용하여 RF 신호를 처리하였다.

Fig. 3은 RF 레코더의 SW UI를 나타낸다. 왼쪽 상단부에는 중심/샘플링 주파수, 입력 이득에 대한 값을 입력할 수 있는 탭으로 구성하였다. 기록되는 신호를 보여주는 그래프는 3가지로 구성된다. 상단 첫 번째 그래프는 중심 주파수와 샘플링 주파수에 의해 추출된 목표 주파수 대역 내에 따른 전력을 확인할 수 있는 부분이다. 두 번째 하단 좌측 그래프는 I-Q 데이터에 관련된 부분이고, 마지막으로 세 번째는 시간에 따른 전력 값을 나타내는 그래프이다.

3. RF 신호처리 소프트웨어 설계

3.1 RF recorder SW

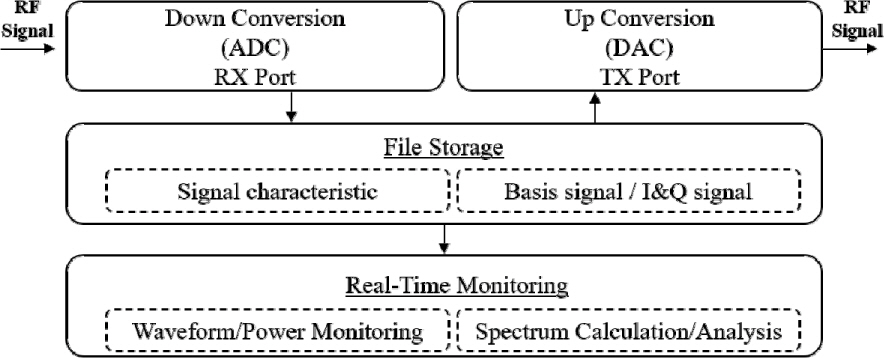

RF 레코더 소프트웨어는 크게 저장/재생 모드 두가지 방식으로 동작 가능하도록 설계되었다. 첫 번째 저장모드는 입력되는 신호를 VST를 거쳐 I-Q 데이터를 획득하며, I-Q 데이터를 디스크에 신호 특성에 따라 분류하고 저장하는 기능을 수행하도록 하였다. 두 번째 재생모드의 경우 실시간 모니터링 기능에 초점을 맞추어 입력되는 신호의 상태를 일정한 주기로 측정 및 출력하였다. 또한 재생모드에서는 수집된 데이터를 모니터링하는 기능을 함께 구현하였다. RF 레코더의 주요 기능 다이어그램은 Fig. 4와 같다.

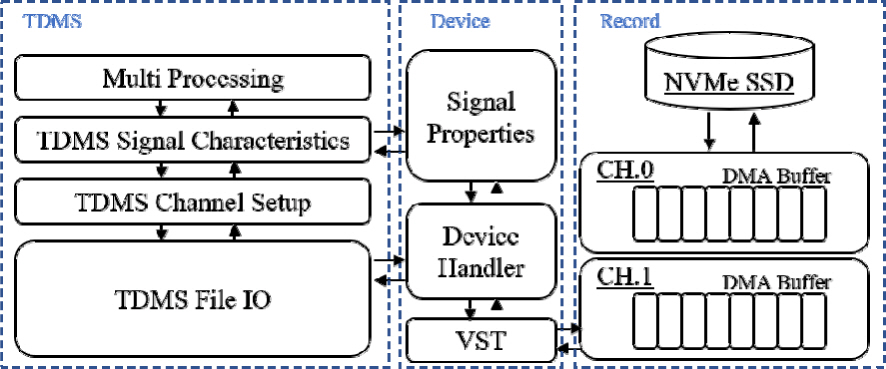

최초 RF 신호는 ADC(Analog Digital Converter)를 통해 Down Conversion 되어 파일 저장소에서 관리 되며, 신호의 실시간 모니터링이 가능하도록 설계되었다. 이때 저장되는 기능 옵션에 따라 파일을 SSD에 별도로 저장하는 기능을 함께 구현하였다. 이후 저장된 데이터를 처리하여 Up Conversion을 통해 신호를 출력시키는 부분까지 구현하였다. SW의 저장/재생모드에 따른 데이터 흐름도를 Fig. 5에서 상세하게 나타내었다. 그림에서 확인되는 TDMS(Technical Data Management Streaming)는 시간 및 데이터 값을 일정 포맷에 맞추어 저장하는 파일구조이며 저장되는 파일 신호 자체 특성과 채널 설정을 통해 Device Handler에서 신호 특성과 함께 파일 입/출력을 담당한다. 이때 Device Handler로 부터 제어되는 데이터는 VST 자체에서 DMA(Dynamic Memory Access)와 SSD에 접근하여 내부 데이터를 관리하도록 데이터 스트림이 설계되었다.

3.2 Simulated target SW

전자표적 SW는 기본적으로 가상의 표적 신호를 생성시키는 목적의 표적생성모드와 저장된 데이터의 신호를 분석하는 재현분석모드로 2가지로 나누어져 설계되었다. 첫 번째로 표적생성모드는 먼저 RF 입력 단으로부터 Pulse와 CW(Continuous Wave) 신호를 획득하는 기능을 한다.

이때 입력 단으로부터 획득된 신호의 시간지연을 발생시켜 거리 지연을 발생시키며, 도플러 주파수를 계산해 속도 모의 기능을 수행한다. 또한 입력된 파라미터 값에 의해 모의 된 신호를 VST를 통해 송출하는 기능을 구현하였다. 두 번째 재현분석모드의 경우에는 기존 RF 입력신호를 통해 저장된 주파수 스펙트럼에 대한 전력 값과 I-Q 데이터 및 시간에 따른 신호의 파형 결과를 출력하는 기능을 구현하였다. Fig. 7은 전자표적 SW 기능의 다이어그램을 나타낸다. 그림과 같이 입력된 RF 신호를 FIFO(First In First Out)의 구조의 메모리에서 처리되며 신호를 Simulating Loop를 통해 실시간으로 모니터링 할뿐 아니라 속도/거리 값등을 기반으로 스펙트럼을 계산하는 기능을 도식화 하였다. 이때 입력된 RF 신호로부터 계산된 주파수 스펙트럼에 대한 데이터는 앞 절의 레코더 소프트웨어와 유사하게 파일 입출력을 통해 저장 가능하다.

Fig. 6은 구현된 전자표적 SW의 UI 화면을 나타낸다. 그림과 같이 상단에 입력된 RF 신호에 대한 주파수 스펙트럼이 나타나 있다. 상단의 그래프 오른쪽으로 거리 모의 지연 거리 설정 값, 모의 속도 설정 값의 입력이 가능한 인터페이스를 나타낸다. 하단 2개의 그래프에서는 각각 신호의 I-Q 그래프와 시간 변화에 따른 신호전력세기를 표현하는 부분이다.

3.2.1 Simulated target range algorithm

본 논문에서 개발된 VST 장비의 거리 모의 기능은 기본적으로 시간지연을 통해 수행되도록 구현하였다. 앞서 언급한 Fig. 8의 그림과 같이 메모리상에서 데이터는 FIFO 형태의 버퍼를 활용하여 신호를 샘플 단위로 지연시킨다. 입력된 데이터에 대한 n번째 샘플이 입력된다고 할 때 버퍼의 길이(L) 만큼 지연시켜 신호를 송출하는 것이 거리모의 알고리즘의 기본원리이다. Fig. 8은 거리모의 알고리즘에 대한 핵심개념을 나타낸다. 그림과 같이 모의가 되기 전 n번째 기본적인 Normal 샘플을 N(n)이라 가정하면 FIFO 형태의 버퍼로 신호가 들어가 길이 L 만큼 지연되어 N(n-L)로 송출된다. 이때 지연시간(Dealy time: td)은 버퍼의 길이와 샘플링 시간(ts)의 곱으로 계산된다.

전자표적 SW에서는 Fig. 6과 같이 샘플 주파수를 설정 할 수 있으므로, 샘플이 발생되는 주기를 fs라고 한다면, 지연시간을 계산하는 방법은 버퍼 길이 L을 fs로 나눈 값이 된다. 예를 들어 표본화 주파수를 1.25 GHz로 설정했다면 샘플 주기는 0.8 ns가 된다. 실제 상황에서는 표적에서 전파가 반사되기 때문에 왕복거리를 생각하면 1개의 샘플 지연을 통해 0.12 m를 지연 시킬 수 있게 된다. 이때 VST의 1개 샘플이 16 bit이므로 4 byte로 구성되기 때문에 125만개를 지연시킨다면 5 MB 용량을 차지하게 된다. VST의 FIFO(First Input First Output memory)가 설정된 5 MB 용량과 일치한다. 즉 1개의 샘플이 0.12 m를 지연시킬 수 있으므로 125만개의 샘플은 최대 150 km를 지연시킬 수 있다.

3.2.2 Simulated target velocity algorithm

본 논문에서 설계된 VST 내 소프트웨어는 속도 모의 기능을 제공하며, 프로그램 내 설정된 속도 값으로 모사하는 신호를 발생시킬 수 있다. 레이다 펄스 신호 및 표적으로부터 반사되는 신호는 고유의 주파수를 가지고 있기에, 표적의 속도는 도플러 주파수를 조절하여 제어할 수 있다. 이때 신호의 파장은 신호의 주파수에 광속을 곱하면 구할 수 있다. 즉 들어오는 신호의 파장이 고정되어있기 때문에, 도플러 효과에 의한 도플러 주파수를 모의하게 되면 표적의 속도가 달라지는 현상을 나타낼 수 있게 된다. GHz 대역의 입력신호는 디지털 영역에서 도플러 모의를 연산하는 것에 비교적 많은 시간이 소요된다. 표본화 주파수와 함께 계산할 연산량이 많기 때문이다. 따라서 주파수를 하향 변환하여 도플러 주파수를 변조한 후, 다시 중심 주파수로 상향 변환하는 과정을 적용해야 한다.

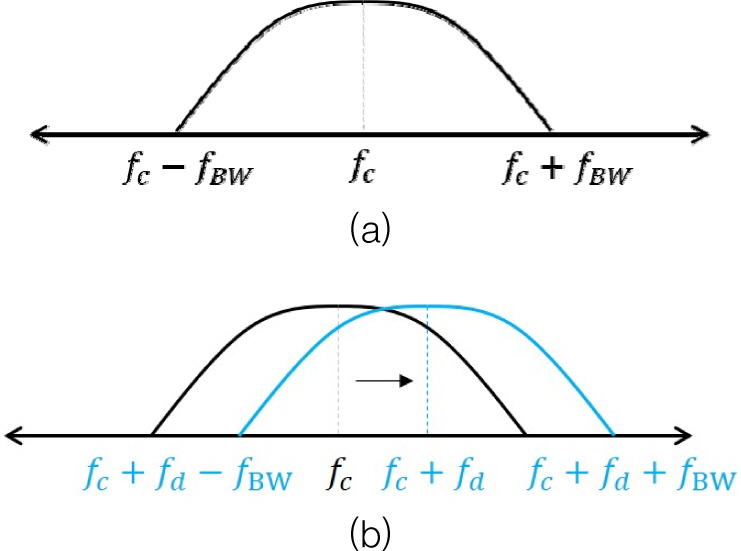

Fig. 9는 속도 모의를 위해 모의전 신호를 기저대역 신호 및 도플러 변조를 적용하는 주파수 대역으로 옮기는 과정을 나타낸다. Fig. 9의 (a)와 같이 모의 전 신호에 대한 신호 스펙트럼을 주파수 대역에서 나타내며, 중심 주파수(fc)를 기준으로 좌/우 fBW의 주파수 대역폭을 갖는다. 이때 신호를 도플러 신호처리 하기 위해 주파수 변화 비율을 도플러 방정식으로부터 정리해보자. 이때 주어진 식에서의 파라미터 값은 fob(Observed frequency), fc(Center frequency), v(Velocity of target), c(Speed of light), fBW(Bandwidth), f0(Transmitted frequency), fd(Doppler frequency) 이다. 식 (1-1)과 식 (*)을 합성하면 식 (1-2)로 정리 된다. 이때 식의 마지막 부분 2v/v*fBW 은 그 값이 작아 생략될 수 있어 식 (1-3)과 같이 정리할 수 있게 된다. 정리된 식에서 2v/c*fc 부분을 fd라고 하고, 그림으로 정리하면 Fig. 9. (b)와 같이 속도에 의해 fd 만큼 주파수가 편이 된다.

속도 변화에 따라 fc + fd가 커질 수 있음을 의미한다. 속도의 방향은 관측되는 지점을 기준으로 멀어지는 방향을 양(+)의 방향이라고 가정한다면, 가까워지는 방향은 음(-)의 방향으로 정의할 수 있다. 예를 들어 타겟의 속도가 관측자로부터 멀어지는 방향으로 움직이면 중심주파수는 왼쪽으로 이동하게 되고, 가까워지는 방향이라면 오른쪽으로 이동하게 된다.

속도 모의를 구현하기 위해 VST 내에서 신호 보간 샘플을 생성하는 개념을 Fig. 10에 나타내었다. 그림의 (a)와 (b)는 각각 속도 모의시 표적과 거리가 멀어지는 경우와 표적과 거리가 시간이 지남에 따라 점차 가까워지는 경우를 나타낸다. Fig. 10의 N[n-1]과 N[n]은 샘플의 개수가 n개라고 가정할 때, 모의 전 샘플의 위치를 나타낸다. 즉 기저 신호에 대한 샘플값의 위치를 나타낸 것이다. 또한 알고리즘을 표현한 그림에서 속도 모의를 위한 샘플을 S’[n]으로 표현하였다. 이는 실제 신호를 속도 모의 하기 위해, 일정 속도를 입력했을 때 신호의 샘플 위치이다. 이때 (a)의 경우 마지막 원신호 샘플인 N[n]와 N[n-1] 중에 모의 샘플이 존재하는 경우로 실제 샘플링이 이루어지는 곳은 S[n] 이다.

따라서 모의 표적과의 거리는 실제보다 길어지게 된다. 이는 거리가 멀어지는 것처럼 신호가 모의 되게 된다. 마찬가지로 (b)의 경우에는 속도 모의된 신호가 N[n] 이후에 그려지는 경우이다. 그렇기 때문에 그림과 같이 S′[n]은 S[n] 우측에 표현되었다. (b)의 경우 (a)와 반대로 그려진 S′[n]에 비해 빠른 S[n]에서 샘플링 되어 원 신호와 비교하여 파장 길이가 짧아지게 된다. 따라서 이 경우에는 모의 표적과 거리가 가까워지는 상황으로 신호가 모의 된다. 이를 수식으로 표현하기 위해 속도 모의신호의 실제 위치 S′[n]와 S[n-1]의 거리를 di라고 두고 원 신호의 샘플사이 간격을 dn이라고 가정하자.

거리가 멀어지는 경우의 개념도인 (a)에서 N[n-1]과 N[n] 지점을 di: (dn - di)로 내분하는 지점을 찾으면 S′[n]의 위치가 된다. 또한 (b)의 경우에서는 N[n-1]과 N[n]을 di - dn으로 외분하는 지점을 찾으면 마찬가지로 S′[n] 이다. 각 내분점과 외분점의 식을 정리하게 되면 식 (2-1)과 같이 정리 된다. 여기서 식의 dt/di 값을 분리하여 (1+R)로 꺼내게 되면, R에 값에 따라 속도 신호 모의 상황을 정리할 수 있게 된다. 이렇게 R에 값에 따라 변조되는 모의 상황을 정리하면 −1<R<0의 범위 내 에서는 모의 표적이 멀어지는 상황으로 파장의 길이가 길어지게 되어 표적과의 거리가 멀어진다. 따라서 속도 값은 양수가 될 것이고, 도플러 주파수는 0보다 작은 음수값으로 계산될 것이다. 마찬가지로 0<R<1 상황에서는 파장의 거리가 짧아지면서 표적과 거리가 가까워지는 상황으로 표적과의 거리가 가까워지고 속도 값은 0보다 작은 음수가 된다. 이 경우 도플러 주파수는 0보다 큰 양수로 계산된다.

3.3 RF environment SW

전파환경 SW는 크게 측정모드와 분석모드로 나누어진다. 먼저 측정 모드의 경우 특정 입력신호에 대하여 관심 주파수 대역의 I-Q 데이터를 수신하여 주파수 스펙트럼 및 대역폭을 분석하며 지정된 복조를 통해 측정한 결과를 출력하는 기능을 구현하였다. 분석모드의 경우 이미 저장된 I-Q 데이터를 바탕으로 주파수, 대역폭, 전력을 기준으로 신호를 분석하고 사용자가 선택한 복조기를 통해 Constellation, Eye Diagram 과 같은 신호패턴을 입력되는 전파환경신호에 따라서 저장 후 데이터를 분석하는 기능을 구현하였다.

Fig. 11. 전파환경 SW의 UI를 나타내며, Fig. 12는 구성된 소프트웨어의 다이어그램을 나타낸다. 상단에는 주파수 대역에서 전력 값과 스펙트럼을 보여준다. 주파수 스펙트럼 예시는 FSK(Frequency-Shift Keying)의 변조 방식의 저장데이터를 재생 중인 화면이며, 하단에는 신호를 시각화하는 Spectrogram이 확인된다.

4. RF신호처리 구현 결과 및 검증

4.1 RF recoder simulation result

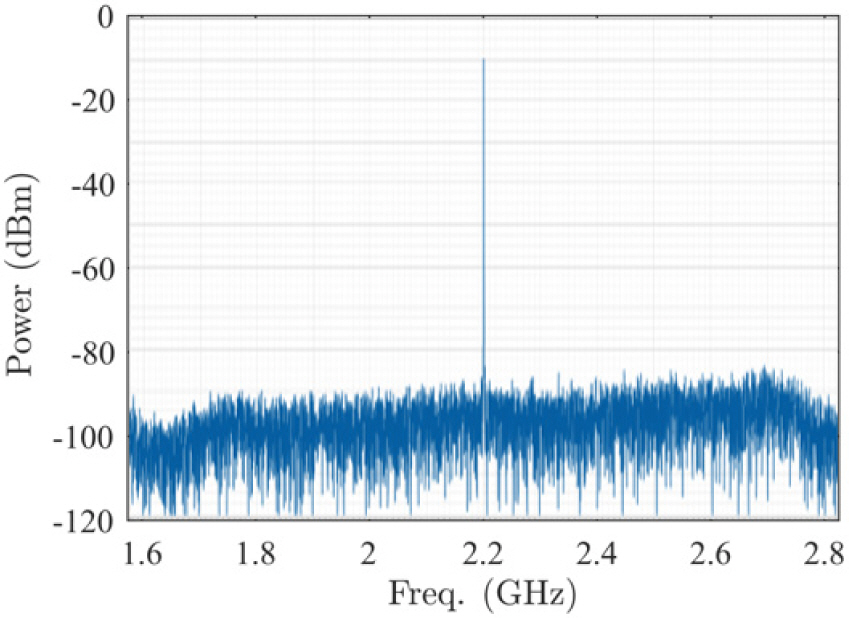

플랫폼에서 섀시를 통해 데이터를 전달 할 때는 DMA에 직접 데이터를 스트리밍 하는 Zero-Copy Data Streaming 방식이 적용되었다. 또한 앞서 언급한 것과 같이 VST 시스템 구조상 RF신호처리를 담당하는 모듈이 2개이므로 채널을 2개를 사용할 수 있다. 따라서 2개의 TDMS 파일 포맷을 채널에 각각 할당하여 저장된 신호를 재생시키고, 일정 주기에 따라 LabVIEW상 VI에 전달하여 신호를 실시간 모니터링 하도록 구현하였다. RF 레코더 소프트웨어를 검증하기 위해 기본적인 정현파 형태의 신호를 입력해주었으며 신호에 입력에 따른 2.2 GHz의 정현파를 입력해주었으며 1.5 GHz의 밴드 내에서 샘플링 하여 그 결과를 Fig. 13과 같이 확인 하였다. 입력된 신호의 전력(Power)는 그림과 같이 −10 dbm 세기의 신호를 입력해주었다.

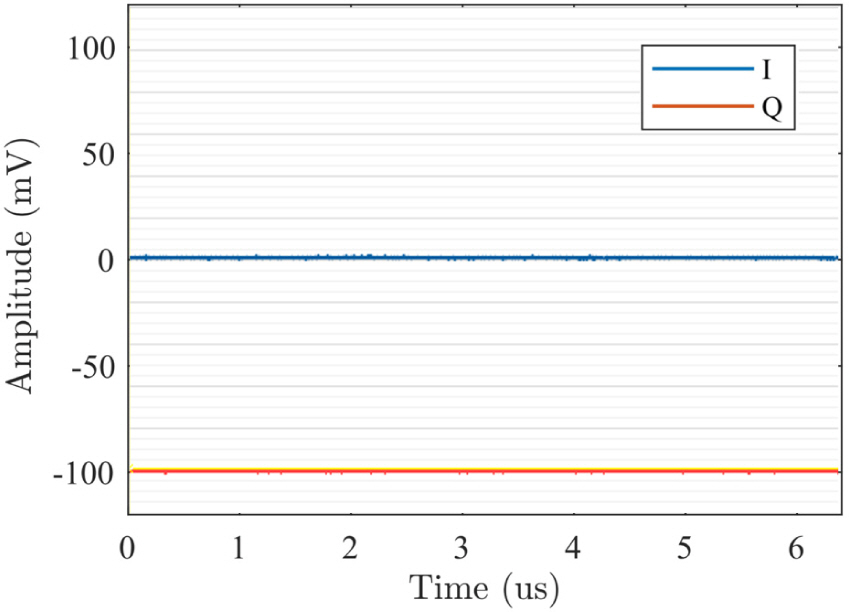

RF 레코더 소프트웨어에서는 기본 정현파로 입력되는 신호의 I(In-Phase), Q(Quadrature) 그래프를 확인할 수 있는데 그 결과가 Fig. 14에서 나타내었다. 소스원의 전압을 x(t)라고 가정하면 입력되는 값은 x(t) = I cos(2πft)+ Q sin(2πft)의 형태로 I와 Q 진폭 성분을 분리시킬 수 있다. 본 시뮬레이션 에서는 신호를 단순화시키기 위해 정현파 신호에서 I의 값은 0으로 계측되고 Q 값이 −100 mV로 되도록 위상을 조절하여 입력하였다.

4.2 Simulated target range simulation

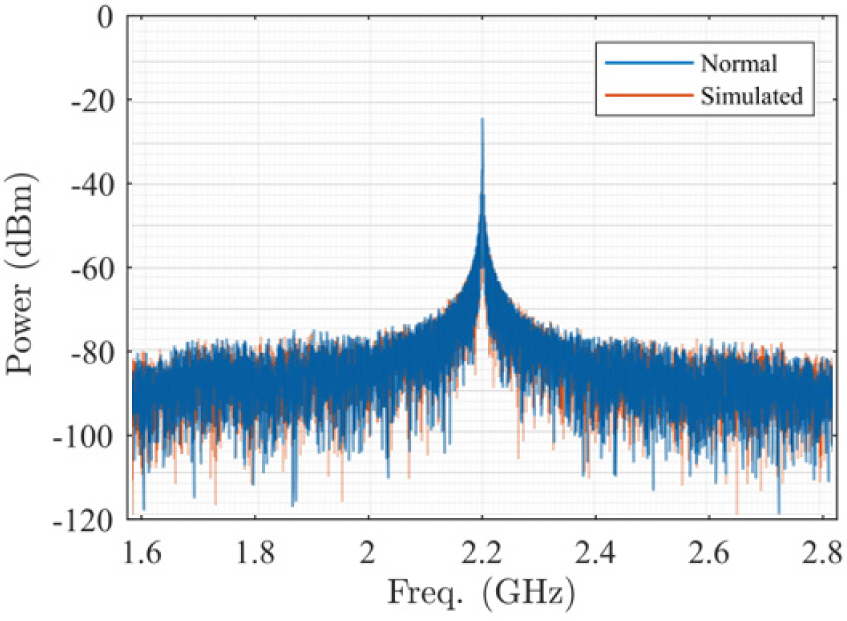

신호발생기로부터 생성된 신호를 앞서 언급한 거리모의 알고리즘을 통해 거리 모의신호를 생성하였다. 이때 입력된 신호는 2.2 GHz의 캐리어 주파수의 정현파 신호의 Pulse 신호가 변조 되었으며, 그 결과가 Fig. 15와 Fig. 16 및 17과 같다. 1.5 GHz의 주파수 밴드 내에서 샘플링을 진행하였기 때문에 Fig. 15와 같이 주파수 대역 내에서 펄스 형태 신호의 주파수성분이 나오는 것을 확인할 수 있다.

시간지연을 통해 입력되는 RF 신호를 지연시켰으며, 그에 따른 결과가 그래프에서 Simulated로 표현된 부분이다. 거리 모의에 경우에는 주파수 스펙트럼에서는 변화가 없기 때문에, Fig. 15와 같이 모의 전/후에 대해 신호의 변화가 거의 없음을 알 수 있다. 반면 시간 축에서 신호를 확인하면 샘플 지연을 통한 신호 거리 지연 효과를 명확하게 확인할 수 있다.

Fig. 16, 17은 모의 전/후에 거리지연이 발생한 그래프를 나타낸다. 먼저 거리 지연이 정상적으로 발생하는지를 검증하기 위해 지연 거리 값을 예시로 들어 시뮬레이션을 진행하였다. 지연거리 49.97 km에서 펄스파가 지연되면서 두 펄스의 위상이 동일 하게 맞춰져 모의 전/후 신호가 겹쳐지는 것을 확인하였다. 이어서 지연거리를 50 km로 맞춰 Fig. 16의 경우와 0.03 km 거리차가 발생하도록 시뮬레이션 하였으며, 그 결과가 Fig. 17과 같다. 앞서 거리모의 알고리즘에서 언급한 것과 같이 위의 시뮬레이션의 경우에 1개의 샘플이 지연시킬 수 있는 거리 모의 값은 0.12 km 이다. 따라서 위 상황의 0.03 km를 지연시키기 위해서는 250개의 샘플지연이 필요하다. 1개의 샘플당 지연시킬 수 있는 시간이 0.8 ns이므로, 250개 샘플을 통해서는 0.2 us 만큼의 시간지연을 발생시킬 수 있다. 즉, 0.03 km의 지연거리 값의 차를 통해 역으로 0.2 us 만큼의 시간지연이 발생함을 시뮬레이션을 통해 검증할 수 있다.

4.3 Simulated target velocity simulation result

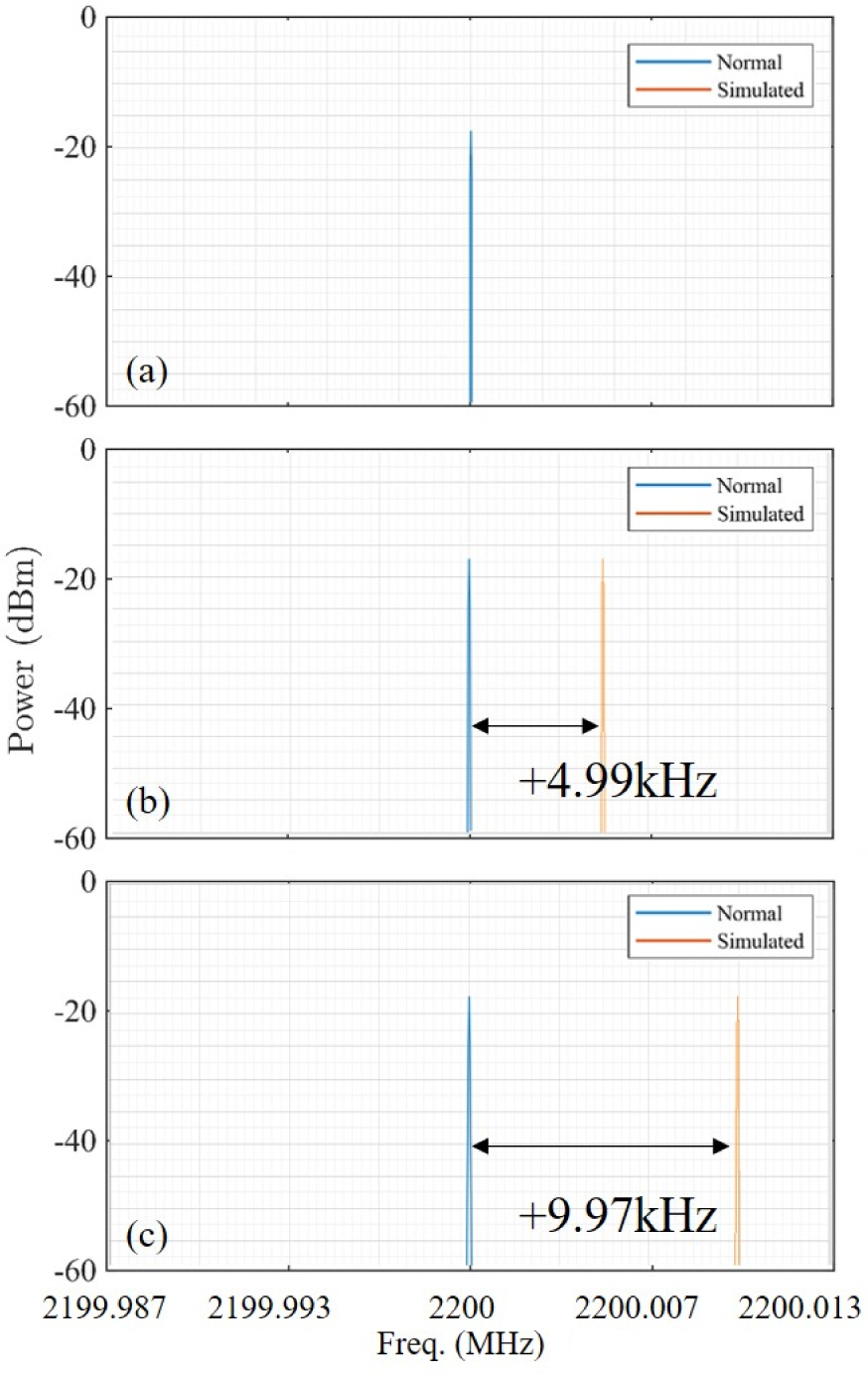

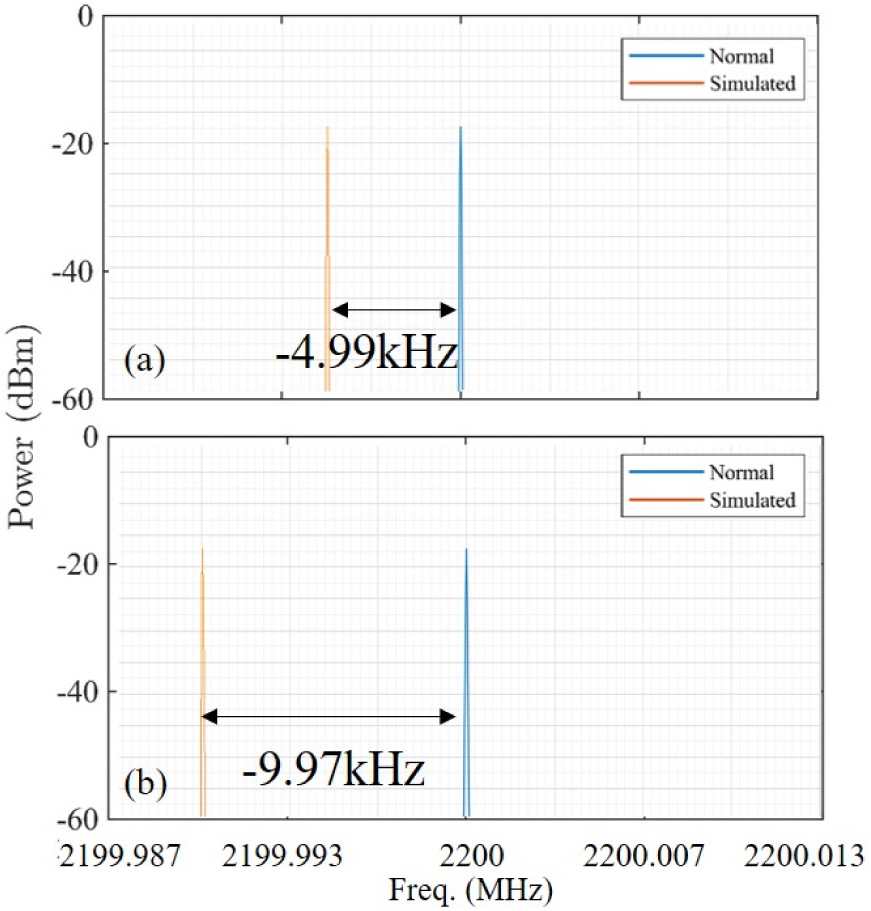

속도 모의 알고리즘을 통해 모의 표적이 속도를 가지고 움직이는 상황을 모의한 결과를 Fig. 18과 19에서 표현하였다. 개발된 모의신호 발생기의 시스템 상 거리가 가까워지는 상황을 경우 음(-)의 속도로 정의하였다. Fig. 18. (a)는 모의 전 기본신호에 대한 그래프로 2200 MHz의 신호가 계측되는 것을 확인 할 수 있다. Fig. 18의 (b)와 (c)는 각각 마하1, 마하2의 속도로 가까워지는 타겟의 신호를 모의한 것으로 도플러 천이 주파수가 각각 +4.99 kHz, +9.97 kHz가 되는 것을 확인하였다. 이는 앞선 3.2.2절의 도플러 주파수(fd)의 값인 fc * 2v/c 으로부터 모의하고자하는 속도 값과 주파수를 대입해보면 정상적으로 주파수 값이 천이되었음을 검증 할 수 있다. 마찬가지로 Fig. 19의 (a)와 (b)는 각각 멀어지는 방향의 마하1, 마하2의 속도를 모의한 것을 표현하였다. 가까워지는 방향의 속도와 절대 값은 동일하기 때문에 모의 전 신호로부터 도플러 천이가 −4.99 kHz, −9.97 kHz 만큼 발생됨을 확인 하였다.

4.4 RF environment simulation

Fig. 20에서는 FSK로 변조된 신호를 I-Q Plot을 표현 하였을 때 그려지는 그래프를 나타낸다. 신호가 샘플링되면서 I-Q Plot의 Constellation 점들이 원형으로 이루어짐을 확인할 수 있다. 추가적으로 BPSK(Binary Phase-Shift Keying) 방식으로 변조된 신호의 특성을 나타낸 결과를 Fig. 21에 나타내었다. Fig. 21. (a)는 BPSK 변조 신호에 대한 주파수 스펙트럼을 나타낸다. 1000 MHz의 fc를 기준으로 20 kHz의 대역폭을 가진 신호임을 확인할 수 있다. BPSK 신호는 신호 생성기를 통해 임의 신호를 생성하여 전파환경 SW에서 분석되도록 입력해주었다. 입력되는 신호는 20 kbps로 Symbol rate를 주었고 전파환경 SW에서 같은 데이터 속도를 입력하게 되면 Fig. 21. (b)와 같이 변조된 BPSK 신호에 대한 Eye diagram을 확인할 수 있다. 그림과 같이 신호의 Noise Margin이 확보되어 해당 전파환경의 신호 품질이 양호하다는 것을 판단할 수 있다.

5. 결 론

본 논문에서는 VST와 FPGA를 이용한 모의 표적 생성 장치에 대해서 제안하였으며, 표적을 생성시키기 위해 LabVIEW 기반의 소프트웨어를 이용하여 신호 생성 및 분석 결과를 제시하였다.

첫 번째로 RF Recorder SW에서는 신호발생기로부터 생성된 데이터 및 안테나로부터 수신되는 신호를 저장 및 관리하기 위한 기능이 구현되었으며, I-Q 데이터 및 주파수 도메인의 신호특성을 확인하였다. 두 번째로 Simulated Target SW에서는 모의 신호를 생성을 위한 방법을 제시하였으며, 표적의 거리와 속도 값을 모의하는 결과를 시뮬레이션 결과를 통해 확인하였다. 펄스 신호의 시간 지연 데이터를 통해 거리 지연 기능을 확인하였으며, 속도 모의 검증을 위해 도플러 방정식으로부터 천이 주파수를 구하는 식을 유도하였다. 또한 가까워지는 방향과 멀어지는 방향 모두에서 마하1/2의 타겟 속도를 모사하여 속도 모의 신호가 정상적으로 발생되는 것을 검증 하였다. 세 번째로 계측되는 신호의 전파환경을 분석하는 기능 구현을 확인하였는데, FSK 및 BPSK의 신호를 입력시켜 I-Q 그래프와 Eye-diagram의 형태를 확인하였다.

본 논문에서 개발된 신호 모의 장치를 통해 특정 위치에 가상의 전자표적을 생성하고 속도를 모의할 수 있으며, 전파환경의 특성을 다양한 관점에서 분석할 수 있는 기능을 확인하였다. 논문을 통해 개발된 장비는 유도무기 시험 및 유·무인 비행체 개발 시험 및 평가 시에 가상의 전자표적을 생성할 수 있다. 이를 통해 교전 시나리오 및 시험과정에 기여할 수 있을 뿐 아니라 무기체계를 탐지하는 레이다를 교란시켜 아군의 생존성과 전자전 능력을 확보시킬 것으로 기대된다. 복잡화되는 무기체계와 현대화전 양상에 따라 모의 교전 시나리오 역시 심도 있는 방향으로 발전되고 있다. 유도무기 및 비행체 이외에도 기타 복합무기 체계가 연계된 특정 모의 교전 상황에서 최적화된 모의신호 생성기법이 향후 과제로 남아있다.