서 론

유도무기에서 파이로는 다양한 방식으로 사용된다. 첫째, 파이로는 발사관에 유도무기를 고정하기 위한 탄 구속 장치 및 부스터를 분리시키기 위해 폭발볼트 를 점화화는 목적으로 사용된다. 둘째, 유도무기 내부장치에 필요한 전원을 공급하는 열전지나 유도무기가 추진력을 얻기 위한 부스터를 점화시키기 위해 착화기를 점화 화는 목적으로 사용된다. 마지막으로 산소, 연료, 유압 등을 공급 개방하고 차단하기 위한 파이로 밸브를 점화시키는 목적으로 사용된다. 이러한 파이로는 요구되는 전류를 일정 기간 공급하여 파이로가 점화하도록 설계된다. 파이로는 주로 ESA Standard Initiator(ESI)를 사용하며, 점화하기 위해서는 10 ms 동안 5.0 A 이상의 일정 전류를 흘려 주어야 한다[1]. 이때, 요구되는 전류를 일정 기간 공급하여 점화 하기 위한 회로를 스퀴브 회로(Squib Circuit)라고 한다[1,2].

스퀴브 회로는 크게 기계식 및 전자식 스퀴브 회로로 나뉜다[1]. 기계식 스퀴브 회로는 전류를 보내기 위한 스위칭 회로로 기계식 릴레이가 사용된다. 이는 초기 상태에 파이로를 확실히 단락시켜 고 안정성을 보장하지만, 진동에 취약하다. 최근에는 이러한 단점을 보완하고자 신뢰성을 고려한 전자식 스퀴브 회로를 사용한다. 스위칭 회로로 Metal Oxide Semiconductor Field Effect Transistor(MOSFET)과 Bipolar Junction Transistor (BJT)인 트랜시트러를 이용하는 전자식 스퀴브 회로는 크게 정전압 회로와 정전류 회로로 구분된다. 정전압 회로는 전류제한저항과 파이로가 직렬로 연결되어 있으며, 전압 및 전류제한저항을 통해 원하는 출력 전류를 만들어 파이로에 공급한다. 하지만 이는 파이로까지의 배선 길이 및 커넥터에 의한 저항값 변화로 전류 값이 변할 수 있음을 의미한다. 탄내 배선은 보통 American Wire Gauge 22(AWG22)을 사용하며, AWG22의 저항도는 52.96 Ω/km이다[3]. 적용하는 시스템에 따라 배선의 길이는 최대 10 m까지 다양하며, 이는 최대 약 0.53 Ω의 편차가 나타날 수 있다. 또한 배선 간의 커넥터를 포함하면 저항값이 최대 약 2 Ω 정도의 차이가 날 수 있다. 따라서 다양한 배선 길이(1 Ω ~ 3 Ω)에 동일한 스퀴브 회로를 사용하기 위해선 저항값의 변동에도 전류의 변동이 없는 정전류 회로가 유리하다.

이러한 장점을 바탕으로 현재 특정 시스템에서 N MOSFET과 NPN BJT로 구성된 정전류 회로를 사용하고 있다[4]. 그러나 기 스퀴브 회로는 파이로의 안정성을 위해 파이로가 N MOSFET의 소스(Source)단과 그라운드(Ground) 사이에 연결되어 있다. 이러한 설계는 타 시스템에 적용 시 파이로까지의 달라진 배선 길이에 의한 저항 변화로 전류가 변하는 점이 발견되었다.

본 논문에서는 기존 점화 회로의 분석을 통해 배선길이(저항의 크기)에 따른 전류가 변하는 문제점을 분석하고, 배선의 길이에도 전류가 변하지 않고 현재 시스템에 맞는 점화 회로를 제안하였다. 제안된 회로는 P형 MOSFET과 PNP BJT로 구성되었으며, 회로의 성능은 시뮬레이션 및 실제 측정을 통해 검증하였다.

기존 스퀴브 회로 분석

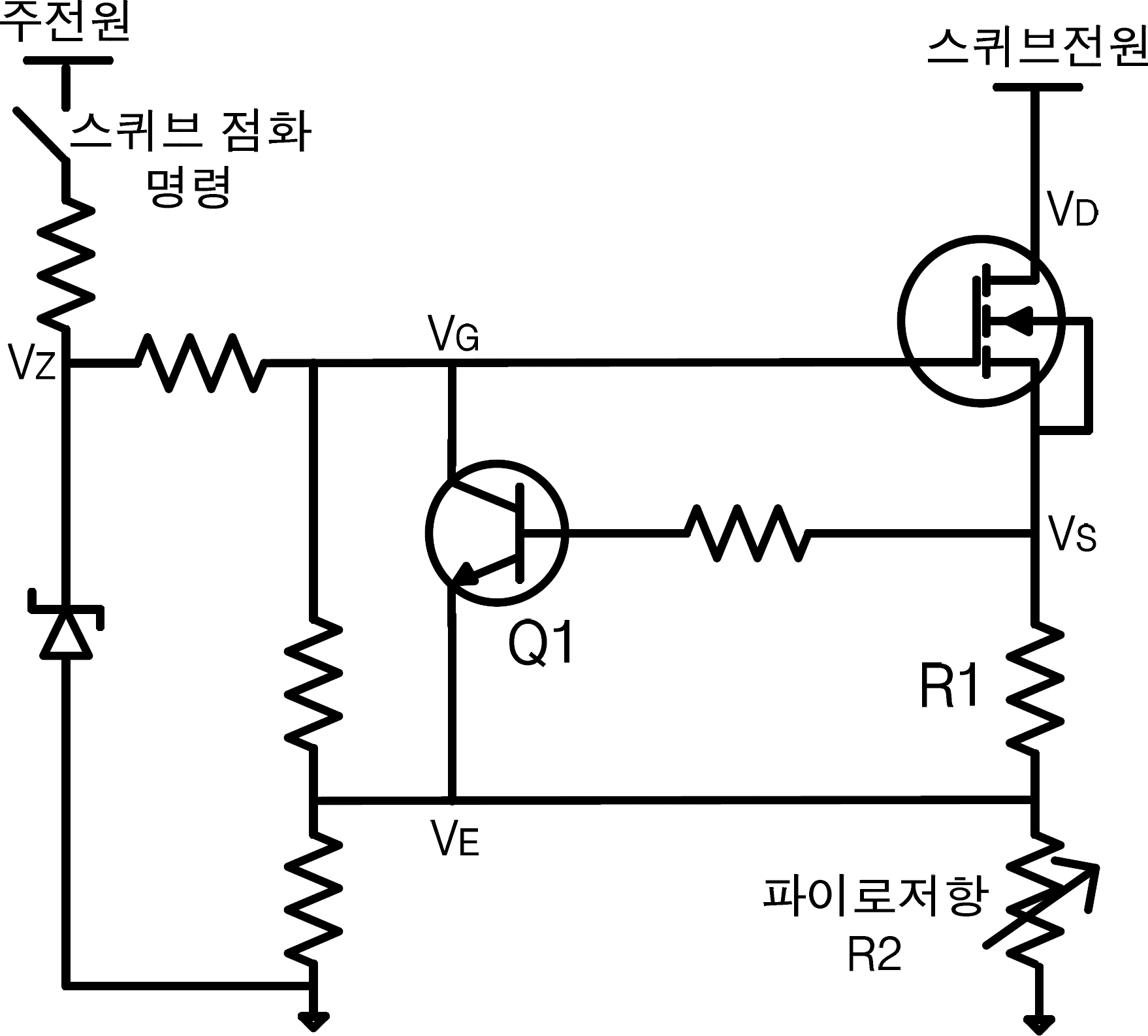

Fig. 1은 N MOSFET과 NPN BJT를 이용하여 설계된 기존 파이로 스퀴브 회로의 개념도이다. 파이로와 배선 및 커넥터의 총 저항을 파이로저항 R2로 나타내었다. 스퀴브 회로는 스퀴브 점화 명령이 인가되면 주 전원을 통해 MOSFET의 VG 전압이 인가되어 포화(Saturation) 영역에서 동작하게 되며, BJT는 활성(Active) 영역에서 동작하게 된다. Active 영역의 BJT 는 저항 R1 사이의 전압 VSE가 VBE,Sat로 고정된다. 따라서 스퀴브 저항으로 흐르는 전류는 식 (1)과 같이 계산된다[4,5].

그러나 식 (1)은 파이로저항 R2가 없을 때 만족하는 식이다. 파이로저항 R2가 커질수록 파이로저항의 전압강하 증가에 의해 VE가 증가하며, BJT의 베이스(Base)와 에미터(Emitter) 양단 전압을 VBE,Sat으로 유지하기 위해 VS는 VE를 따라라서 증가한다. MOSFET의 VG 역시 제너다이오드의 VZ 전압까지 VS가 증가한 만큼 증가하여 VGS는 변하지 않는다. VS의 증가는 식 (2)의 Body Effect에 의해 문턱전압 Vth의 증가를 초래한다.

여기서 Vt0는 초기 문턱전압이며, α는 바디 효과 계수를, Vsb는 substrate와 body와의 전압 차이를 의미한다.

따라서 Vth가 증가하므로 MOSFET의 Saturation 식 (3)에 의해 파이로 저항에 흐르는 전류가 작아지게 된다.

식 (3)에서 un은 전자의 이동로를, Cax는 oxide의 Capacitance를, W와 L는 각각 채널의 Width와 Length 를 의미하며 MOSFET의 고유 특성이다.

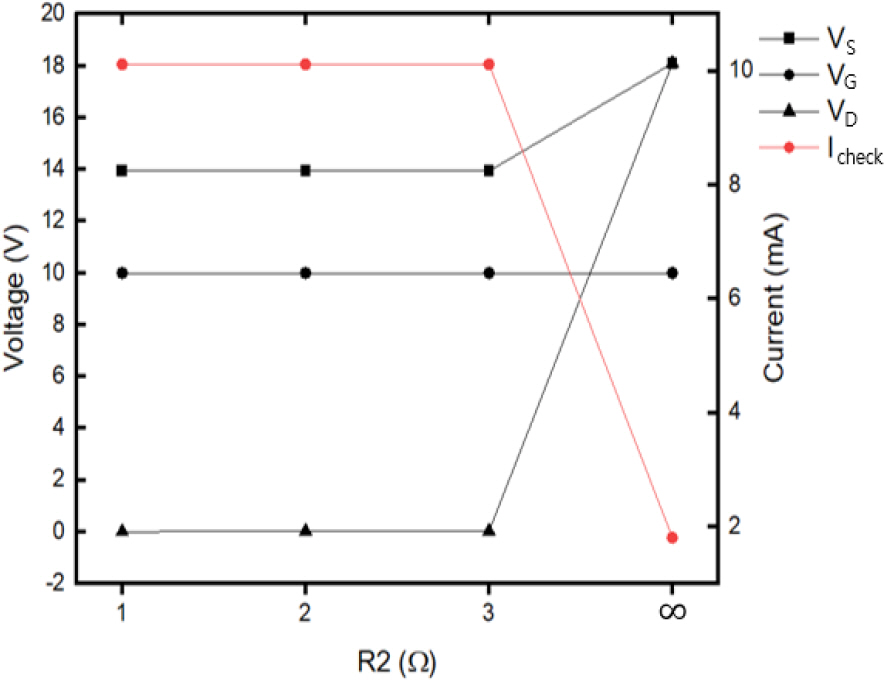

Fig. 2는 점화 명령을 인가하였을 때, 파이로저항 R2값에 따른 스퀴브 회로의 각 노드 전압과 파이로저항 R2에 흐르는 전류량을 시뮬레이션한 그림이다. 파이로저항 R2 값은 배선 및 커넥터를 고려하여 1 Ω, 2 Ω, 그리고 3 Ω으로 선정하였다. 총 저항값이 커짐에 따라 VG, VS 그리고 VE, 전압 모두 증가하였으며, 파이로저항 R2에 흐르는 전류는 감소하였다. R2가 1 Ω 일 때 전류는 5.23 A, 2 Ω 일 때 전류는 4.83 A, 3 Ω 일 때 전류는 3.94 A로, 최대 저항이 3 Ω일 때 전류량이 최소 저항 1 Ω에 비해 약 25 % 줄어들었음을 확인할 수 있다.

Fig. 2.

Simulation of each node voltage and current with existing squib circuit for changing pyro resistance

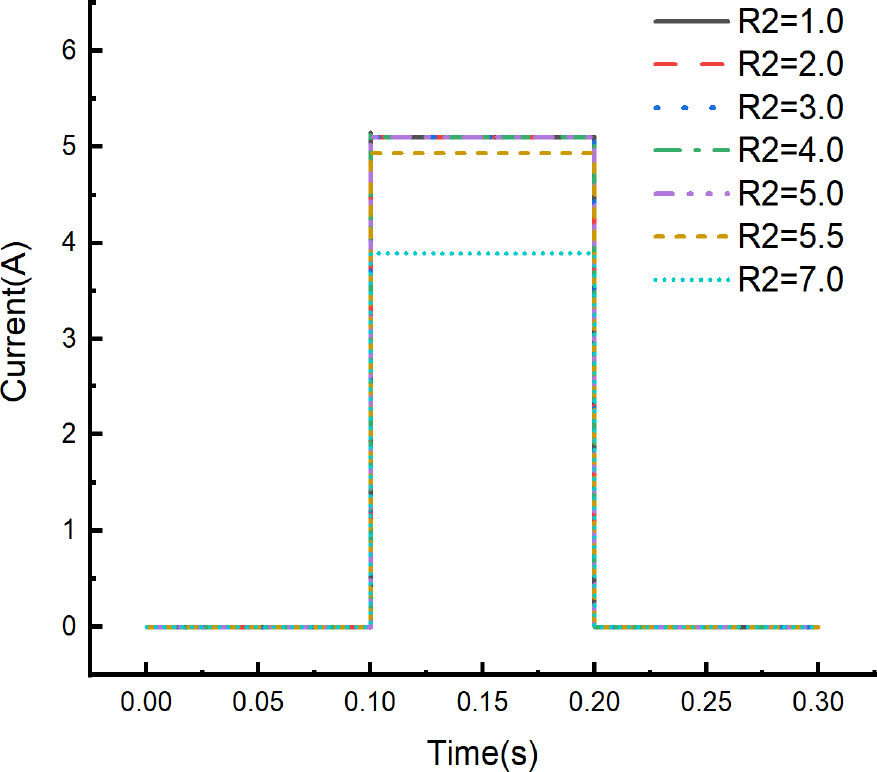

이러한 전류의 변화를 막기 위해 Fig. 3과 같이 파이로 저항을 N MOSFET의 Drain에 연결할 수 있다.

동작 시 Q1 BJT는 Active 영역에서 동작하여 저항 R1 사이의 전압 VSE가 VBE,Sat으로 고정되기 때문에 N MOSFET의 Drain 전압값에 상관없이 식 (1)과 같이 일정한 전류가 흐르게 된다.

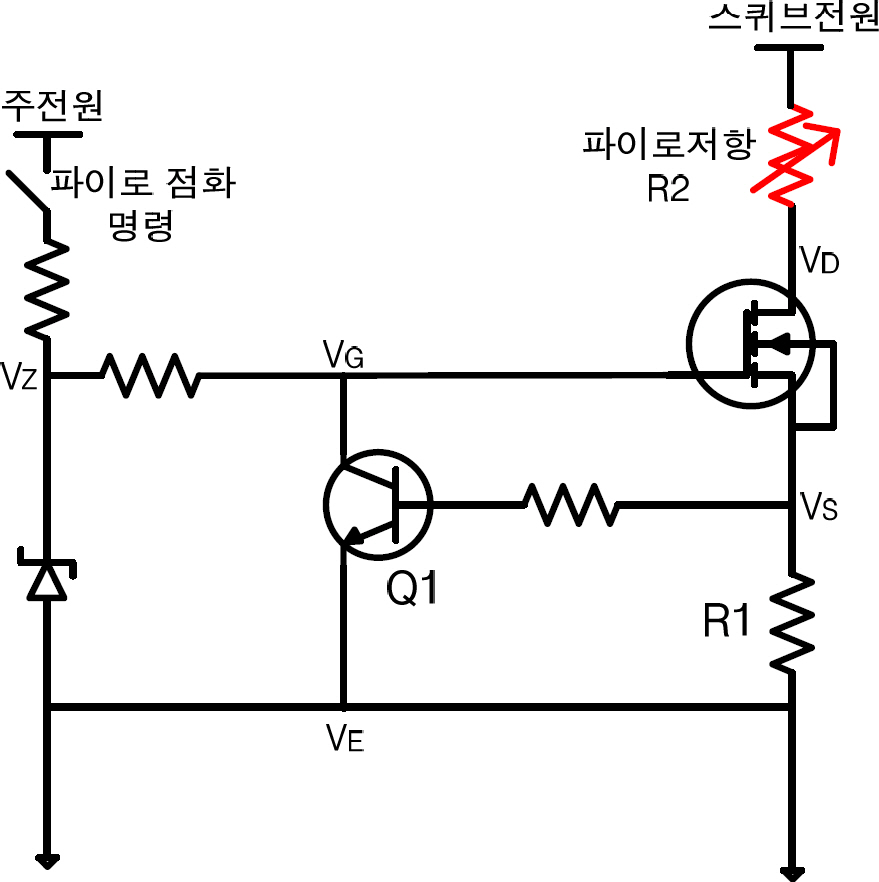

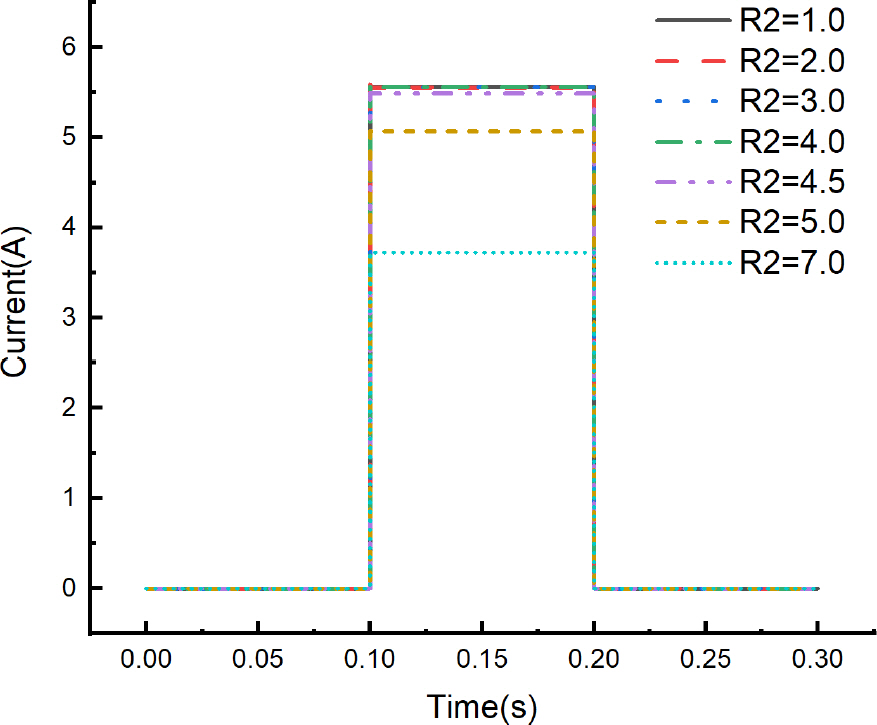

Fig. 4는 시간에 따른 전류값을 시뮬레이션한 그림이다. 파이로 점화 명령을 0.1 s 부터 0.2 s 까지 총 0.1 s 동안 인가하였을 때 파이로저항에 흐르는 전류값을 측정하였다. 전류는 파이로저항값이 5.0 Ω까지 변하지 않았으며 그 이상부터 전류가 줄어듬을 확인할 수 있다.

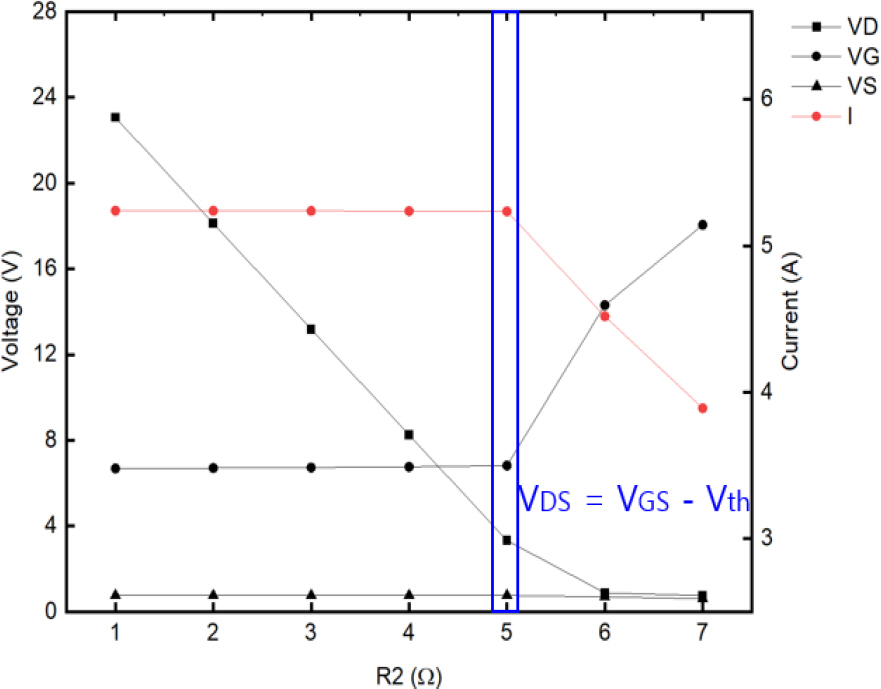

Fig. 5는 점화 명령을 인가하였을 때, 파이로저항 R2 값에 따른 스퀴브 회로의 각 노드 전압과 총 저항에 흐르는 전류량을 시뮬레이션한 그림이다. 파이로저항 R2값이 커짐에 따라 양단 전압강하가 커지므로 N MOSFET의 Drain 전압 VD가 작아진다. 하지만 N BJT Q1은 Active 영역으로 동작하여 VSE가 VBE,Sat으로 고정되어 식 (1)과 같이 동일한 전류가 흐른다. 전류는 스퀴브저항 R2가 1 Ω 부터 5 Ω까지 일정하며, 이는 N MOSFET이 VDS > VGS – Vth를 만족하는 Saturaion 영역에서 동작하는 구간이다. 저항값이 5 Ω 이상이 되면 VDS < VGS – Vth를 만족하게 되어 N MOSFET이 Linear 영역에서 동작하며 전류가 감소하게 된다. 저항값이 커질수록 N MOSFET은 점점 Linear 영역이 깊어지며 전류는 작아진다.

Fig. 5.

Simulation of each node voltage and current with resistor R2 connetced to N MOSFET drain for changing pyro resistance

이러한 시뮬레이션을 통해 파이로 저항을 N MOSFET 의 Drain에 연결하면 조건 저항(1 Ω ~ 3 Ω)내에서 안정적인 정전류 회로로 동작함을 확인할 수 있다.

하지만 이러한 회로 구성에는 안정성 측면에서 취약점이 존재한다. 스퀴브저항이 전원 단에 배선을 통해 연결되면 미사일이 비행 도중 큰 충격 등 불의의 사고로 인해 배선이 접지에 단락될 시 파이로에 큰 전류가 흘러 스퀴브 점화 명령 없이도 파이로가 점화 될 수 있다. 또한 점검 회로 단을 이용할 수 없어 파이로가 정상 장착이 되어 있는지 확인이 불가능하다. 이러한 이유로 파이로는 전원 단에 연결되어 있지 않고 접지에 연결되어 있는 것이 바람직하다. 이에 따라 본 논문에서는 파이로가 접지에 달린 안정적인 정전류 회로를 제안하였다.

안정적인 정전류 스퀴브 회로

3.1 제안한 회로 및 동작

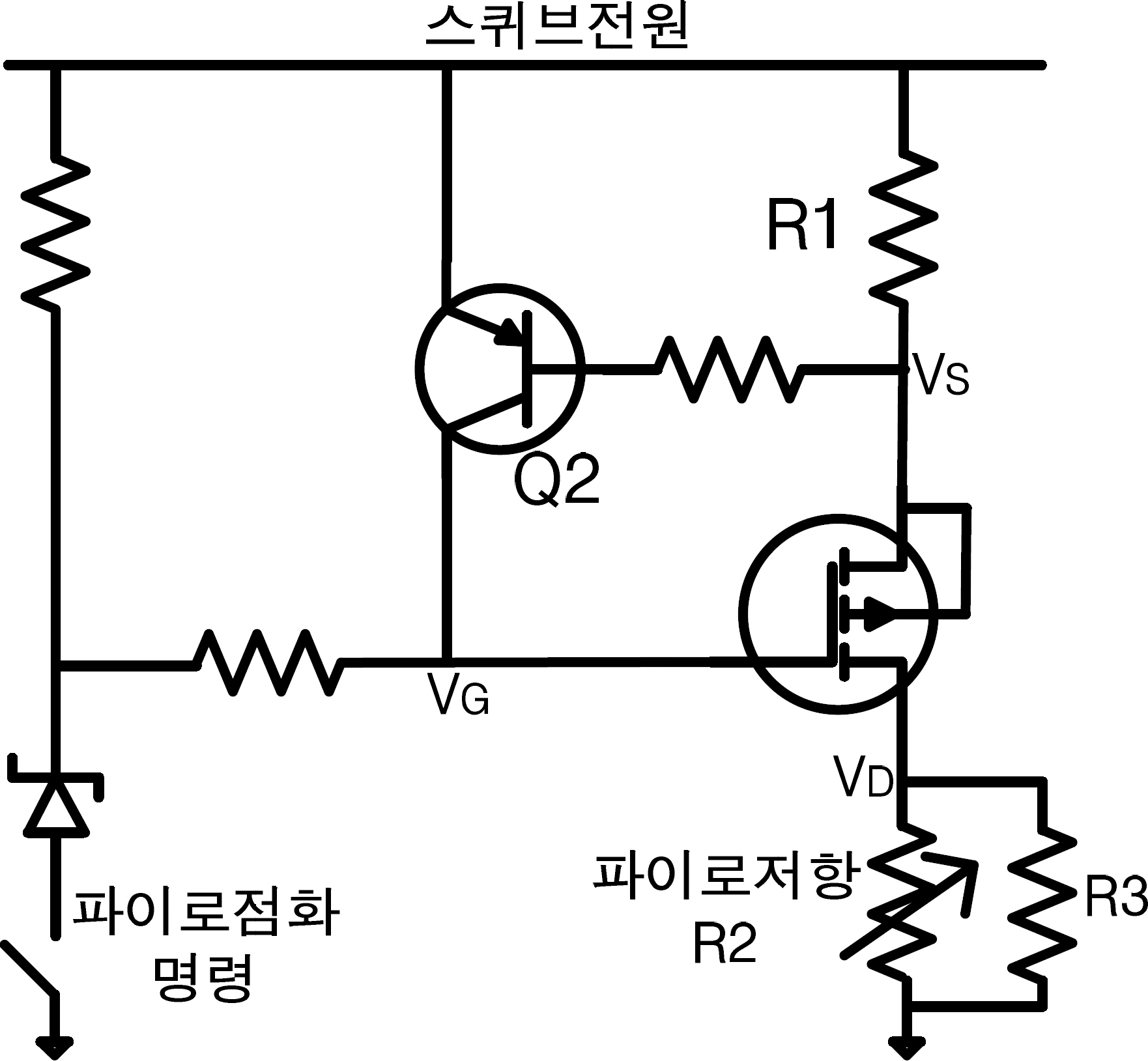

Fig. 6은 본 논문에서 제안한 안정적인 정전류 스퀴브 회로의 개념도이다. 파이로를 접지에 연결하기 위해 P MOSFET과 PNP BJT를 이용하여 스퀴브 회로를 구성하였다.

회로 동작은 N MOSFET과 N BJT로 구성된 스퀴브회로와 유사하다. 파이로 점화 명령이 오기 전에는 P MOSFET의 Gate 전압에 스퀴브 전원이 그대로 인가되어 P BJT 및 P MOSFET이 turn off 되어 있다. 파이로 점화 명령이 들어오면 제너 다이오드와 저항에 의해 P MOSFET의 Gate 전압이 인가되어 turn on 되어 Saturation 영역으로 동작하게 된다. P BJT는 Active 영역으로 동작하게 되어 R1 양단 전압이 VEB,Sat 고정된다.

따라서 파이로 저항에 흐르는 전류 식은 식 (4)와 같다.

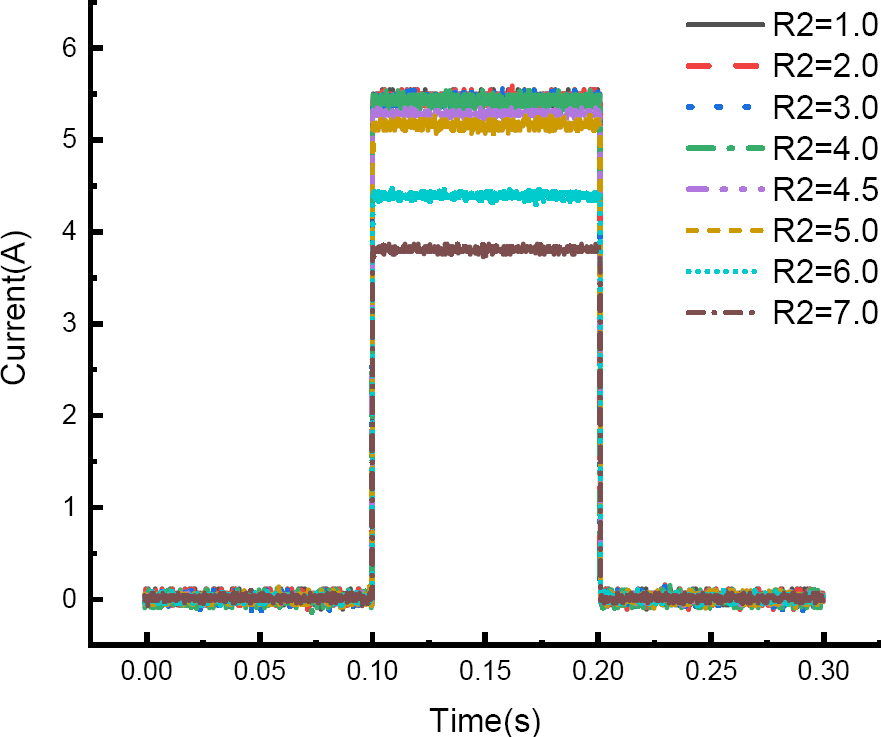

Fig. 7은 제안된 스퀴브회로의 시간에 따른 시뮬레이션 그림이다. 파이로저항 R2 값을 변화시키며 측정한 전류 그래프이다. 0.1 s부터 0.2 s까지 총 0.1 s 동안 스퀴브점화 명령을 인가하여 파이로저항에 흐르는 전류를 측정하였다. 파이로저항 R2가 1 Ω부터 4 Ω까지 약 5.56 A의 동일한 전류가 흐르며, 저항이 4 Ω 이상으로 커질수록 전류가 줄어듦을 확인할 수 있다.

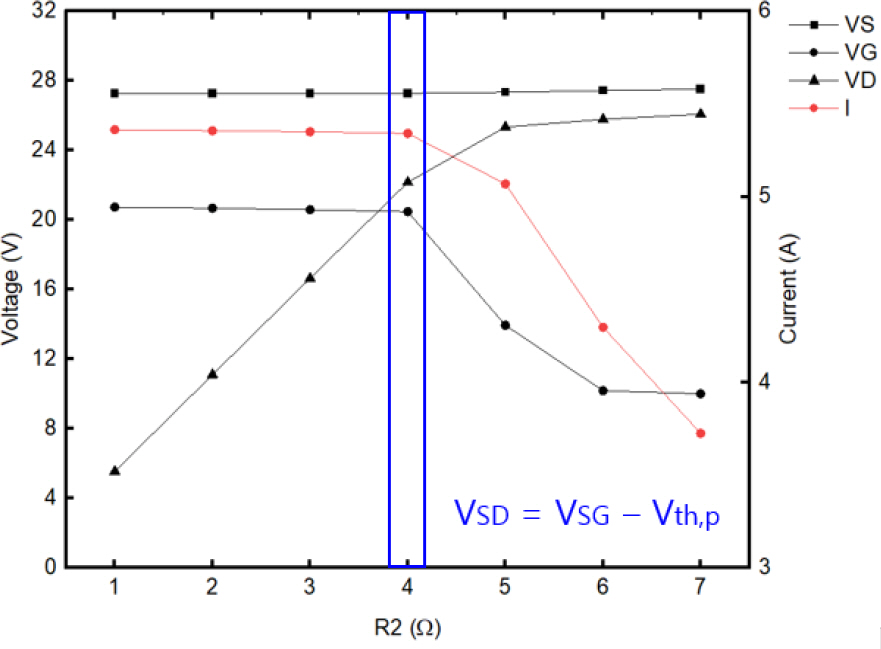

Fig. 8은 점화 명령을 인가하였을 때, 파이로저항 R2 값에 따른 점화 회로의 각 노드 전압과 파이로저항에 흐르는 전류량을 시뮬레이션한 그림이다. 파이로저항 R2가 커짐에 따라 전압강하에 의해 P MOSFET의 Drain 전압 VD가 증가한다. 파이로저항이 4 Ω 이하일 때 P MOSFET이 포화영역에서 동작하기 위한 조건 VSD > VSG – Vth를 만족하여 일정한 전류가 흐른다. 파이로저항 R2가 4 Ω 이상에서 VSD < VSG – Vth를 만족하여 P MOSFET이 포화영역에서 벗어나 Linear 영역에 빠져 전류가 작아진다.

Fig. 8.

Simulation of each node voltage and current with the proposed squib circuit for changing pyro resistance

이러한 시뮬레이션을 통해 저항 변화의 요구 조건(1 Ω ~ 3 Ω)에서 정전류 동작을 확인하였다.

3.2 점검 회로

파이로의 점화 실패는 임무 실패를 의미하기 때문에 유도무기를 발사하기 전 스퀴브회로의 상태를 점검하는 것이 중요하다. 점검은 파이로가 점화되지 않을 정도의 작은 전류(Icheck)를 이용하여 스퀴브회로의 정상상태를 확인한다.

점검용 전원을 통해 스퀴브전원에 전원이 인가된 후, 점화 명령을 인가하면 파이로 저항이 기폭 되지 않을 작은 전류를 흘려 lookup table을 통해 만든 VD 값을 비교하여 스퀴브 회로 정상 동작 및 파이로의 유무를 확인한다.

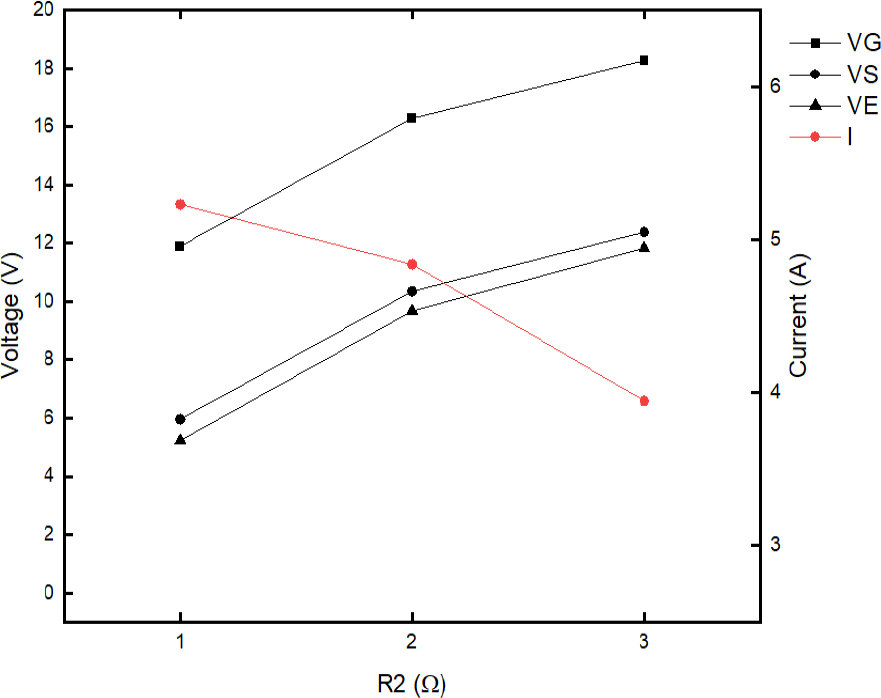

Fig. 9는 점화 명령을 인가하였을 때, 파이로 저항 크기에 따른 각 노드의 전압 및 파이로 저항에 흐르는 전류량 시뮬레이션한 그림이다. 파이로 저항이 정상적으로 연결되어 있을 때(1 Ω ~ 3 Ω)와 파이로 저항이 정상적으로 연결되지 않을 때(∞Ω)의 전압 및 전류값을 나타내었다.

1 Ω ~ 3 Ω의 파이로 저항이 달려 있을 경우, 작은 점검용 전원에 의해 P BJT는 약간의 turn on이 되고, P MOSFET은 3.94 V의 VSG와 13.93 V의 VSD에 의해 Saturation 영역에서 10.12 mA의 전류를 흘리게 된다. 이때의 VS는 약 13.94 V이며, VD는 10.12 mV이다. 파이로 저항이 커져도 VS와 VG는 같으며 같은 전류가 흐르게 되지만 VD는 커지는 파이로 저항에 의해 값이 약간씩 증가하며 3 Ω 일 때 약 30.35 mV이다.

파이로 저항이 정상적으로 달려 있지 않은 경우, 점검용 저항 R3에 의해, P BJT는 tun off 되고 P MOSFET은 8.09 V 크기의 VSG 및 0.001 V 크기의 작은 VSD에 의해 Linear 영역에서 1.81 mA의 전류를 흘린다. 이때의 VS는 약 18.095 V이며, VD는 18.094 V다.

lookup table을 통해 만든 VD값을 비교하여 스퀴브회로의 정상 동작 및 파이로의 유무를 확인할 수 있다.

제작 및 측정

Fig. 10은 실제 제작된 PMOS 스퀴브 회로와 이를 측정하기 위한 환경 세팅이다. 회로 제작은 실제 환경과 같이 1 채널에 2개의 점화 회로를 설계하였으며 1개의 스퀴브 회로를 측정하였다. 실험은 파이로 저항을 1 Ω 부터 7 Ω 까지 1 Ω 간격으로 증가시키며 오실로스코프를 이용하여 저항에 따른 전류 및 P MOSFET의 각 단 전압을 측정하였다.

Fig. 11은 시간에 따른 파이로 저항의 크기를 변화시키며 파이로 저항에 흐르는 전류를 측정한 그림이다. 파이로 점화 명령을 0.1 s 시간 동안 인가하여 파이로에 흐르는 전류를 측정하였다.

파이로 저항이 1 Ω부터 3 Ω까지 약 5.44 A의 동일한 전류가 흘렀으며, 4 Ω시 약 5.40 A로 미세하게 전류가 줄기 시작하였다. 파이로 저항이 4.5 Ω 시 전류는 5.29 A, 5.0 Ω 시 전류는 4.90 A, 6.0 Ω 시 전류는 4.33 A, 마지막으로 7.0 Ω 시 3.72 A의 전류가 각각 측정되었으며, 4.5 Ω부터 전류가 급격히 줄어들기 시작하였다.

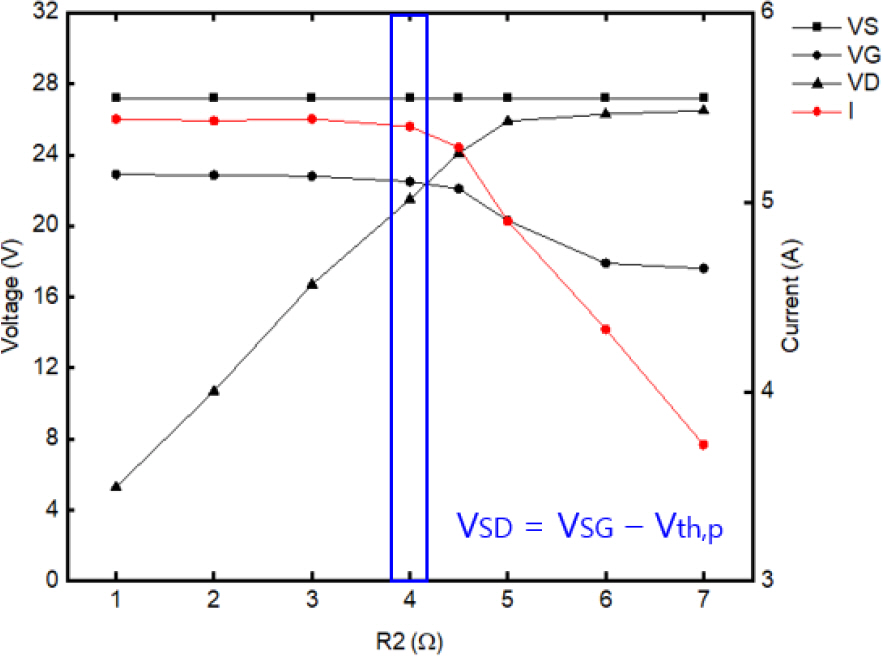

Fig. 12는 스퀴브 회로를 점화시켰을 때 파이로 저항값에 따른 P MOSFET의 각 단 전압 및 전류이다.

Fig. 12.

Measurement of each node voltage and current with the proposed squib circuit for changing pyro resistance

파이로 저항이 4.0 Ω 이전에는 VSD 값이 VSG 값보다 커 P MOSFET이 Saturation 영역에서 동작하여 식 (4)와 같이 동일한 전류가 측정되었다. 파이로 저항이 커져 4.5 Ω에 도달했을 때, VSG 값이 VSD 보다 커지며, 이로 인해 P MOSFET이 Saturation 영역에서 벗어나 Linear 영역에 빠지게 되어 전류가 줄어들기 시작한다. 이는 파이로 저항이 커질수록 더 깊은 Linear 영역으로 빠지게 되며 전류는 더욱 줄어들게 된다. 시뮬레이션과 동일한 본 실험 결과를 통해 PMOS를 이용한 정전류 회로가 정상 동작함을 확인하였다.

다음으로 Table 1은 점검회로단의 측정 결과이다. 탄내배선을 고려하여 파이로저항을 1 Ω과 3 Ω 사이라 가정하고 실험을 진행하였다. 1 Ω과 3 Ω 모두 약 3.49 V의 VSG와 13.4 V의 VSD에 의해 Saturation 영역에서 약 11 mA의 전류가 측정되었다. 다음으로 파이로 저항이 비정상으로 달려 있는 경우, 10 kΩ 저항에 의해 7.52 V 크기의 VSG 및 0.001 V 크기의 작은 VSD에 의해 Linear 영역에서 1.787 mA의 전류가 측정되었다. 점검회로단의 기능 역시 시뮬레이션과 동일한 결과를 통해 설계한 의도대로 잘 동작함을 확인하였다.

결 론

본 논문은 기존 점화 회로의 문제점을 제시하고 문제점을 해결하기 위한 새로운 정전류 점화 회로에 관해 기술하였다. 기존 점화 회로는 배선 및 커넥터에 의한 저항 크기의 변화로 파이로 저항에 흐르는 전류가 변하며, 저항 크기변화의 요구 조건(1 Ω ~ 3 Ω) 내에서 최대 25 %가 변화함을 확인하였다. 이러한 문제를 해결하기 위해 제안된 회로는 P MOSFET과 PNP BJT를 이용하여 시뮬레이션 통해 설계되었다. 실제 제작 및 측정을 통해 저항 크기변화의 요구 조건 내에서 저항 크기가 변해도 안정적인 점화 정전류를 파이로 저항에 흘리는 것을 확인하였다.

실제 제작된 정전류 회로는 추후 체계에 적용하여 체계와의 적용성을 검증할 계획이다.