40 W급 고출력 MMIC 개발과 고출력 증폭기 모듈 결합을 통한 Ku 밴드 반도체형 송신기(SSPA) 개발에 관한 연구

Study on the Ku band Solid-State Power Amplifier(SSPA) through the 40 W-grade High Power MMIC Development and the Combination of High Power Modules

Article information

Trans Abstract

In this paper, to substitute the existing TWTA(Travailing Wave Tube Amplifier) component in small radar system, we developed the Ku band SSPA(Solid-State Power Amplifier) based on the fabrication of power MMIC (Monolithic Microwave Integrated Circuit) chips. For the development of the 500 W SSPA, the 40 W-grade power MMIC was designed by ADS(Advanced Design System) at Keysight company with UMS GH015 library, and was processed by UMS foundry service. And 70 W main power modules were achieved the 2-way T-junction combiner method by using the 40 W-grade power MMICs. Finally, the 500 W SSPA was fabricated by the wave guide type power divider between the drive power amplifier and power modules, and power combiner with same type between power modules and output port. The electrical properties of this SSPA had 504 W output power, - 58.11 dBc spurious, 1.74 °/us phase variation, and - 143 dBm/Hz noise level.

1. 서 론

최근 이동 통신 분야에서 데이터 처리 속도를 향상하고, 대용량의 데이터 전송 및 처리를 위하여, 질화물반도체(GaN, Gallium Nitride)를 기반으로 하는 초고주파 및 고출력 전자소자가 많이 개발되고 있다. 이러한 기반 기술을 이용하여 현재 미국과 유럽 등을 중심으로 기존의 레이더 기술에 적용된 고출력 송신 장치인 TWTA(Traveling Wave Tube Amplifier)를 대체하기 위해 반도체형 송신기인 SSPA(Solid-State Power Amplifier)에 대해 많은 연구가 진행되고 있다[1,2]. 국내에서도 전량 수입하여 사용하는 TWT를 대체할 수 있고, 예열 시간 단축과 시스템적 안정성 등의 이유로 SSPA 개발에 관한 많은 연구가 이루어지고 있다.

Table 1은 반도체 소자 제작에 사용되는 여러 가지 물질의 특성을 정리한 것이다. εr는 유전상수, μn는 전도 이동도, νsat는 포화 속도, Θ는 열전도도, Eg는 에너지 간격, 그리고 Ebr는 역방향 항복 전장이다. Table 1에서 확인할 수 있듯이 GaN의 경우 다른 물질보다 비교적 높은 포화 속도와 역방향 항복 전장 특성을 가짐을 알 수 있다. 또한, 특별하게 GaN의 경우 이중접합(Heterojunction) 구조의 성장이 가능하여 800 cm2/Vs보다 높은 전자 이동도를 구현할 수 있다. 이러한 GaN 의 물성적 특성을 이용하여 고주파수 특성과 고출력 특성을 동시에 가지는 전자 소자 구현이 가능하다.

본 논문에서 UMS사의 파운드리 GH015 공정을 통하여 40 W급 GaN MMIC(Monolithic Microwave Integrated Circuit)를 개발하고, 개발된 MMIC를 T-junction 2-way 결합을 통하여 70 W급 모듈을 제작하였다. 이후, 70 W 급 모듈의 도파관 결합을 통하여 최종적으로 500 W급 반도체형 송신기인 SSPA를 개발하고, 그 결과를 정리하였다.

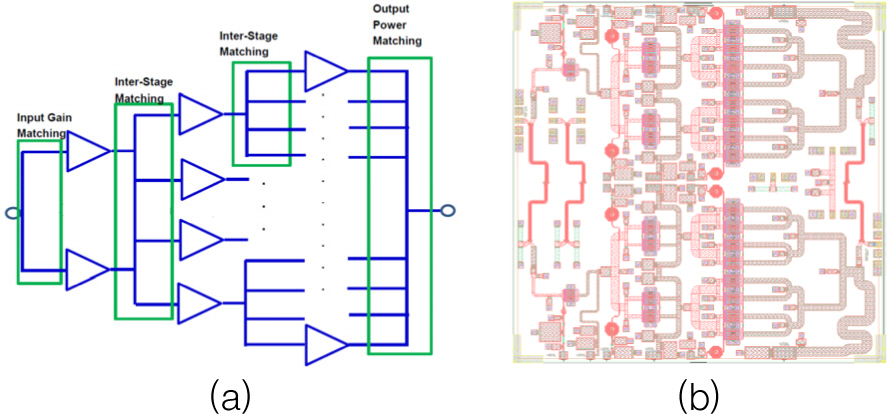

2. 40 W급 고출력 증폭기 개발

40 W급 고출력 MMIC를 개발하기 위해 UMS사의 GH015 공정을 사용하였으며, 게이트 0.15 um의 HEMT (High Electron Mobility Transistor) 소자를 사용하여 설계하였다. Fig. 1(a)는 40 W급 고출력 MMIC 개발을 위한 다단 설계안을 나타낸 것이다. 안정적인 출력을 확보하기 위해, 입력 이득 정합, 각 단계별 정합 그리고 최종단계로 출력 정합을 반영하여 설계하였다. Fig. 1(b)는 UMS GH015 라이브러리를 통해 설계된 40 W급 고출력 MMIC의 설계안을 나타낸 것이다. 20 W급 소자의 2-way 방법으로 결합하는 구조로 설계하였으며, 최종 설계된 칩의 사이즈는 4.655 mm × 4.655 mm이다.

40 W-grade GaN power amplifier, (a) MMIC block diagram, (b) MMIC layout(20 W 2-way combine structure)

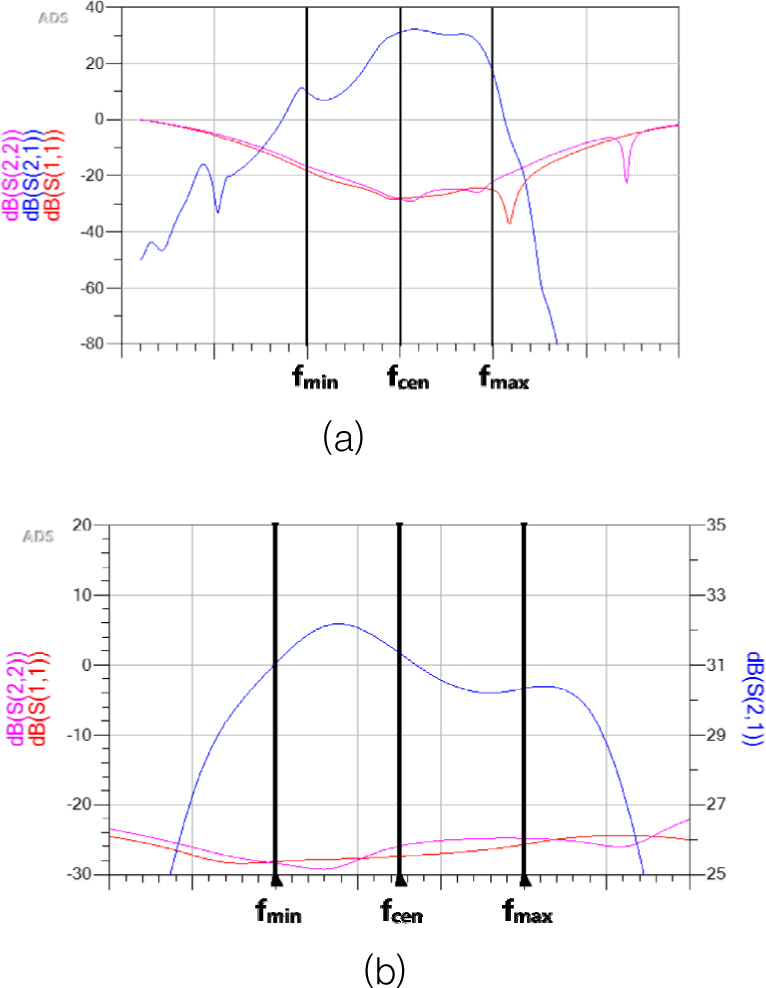

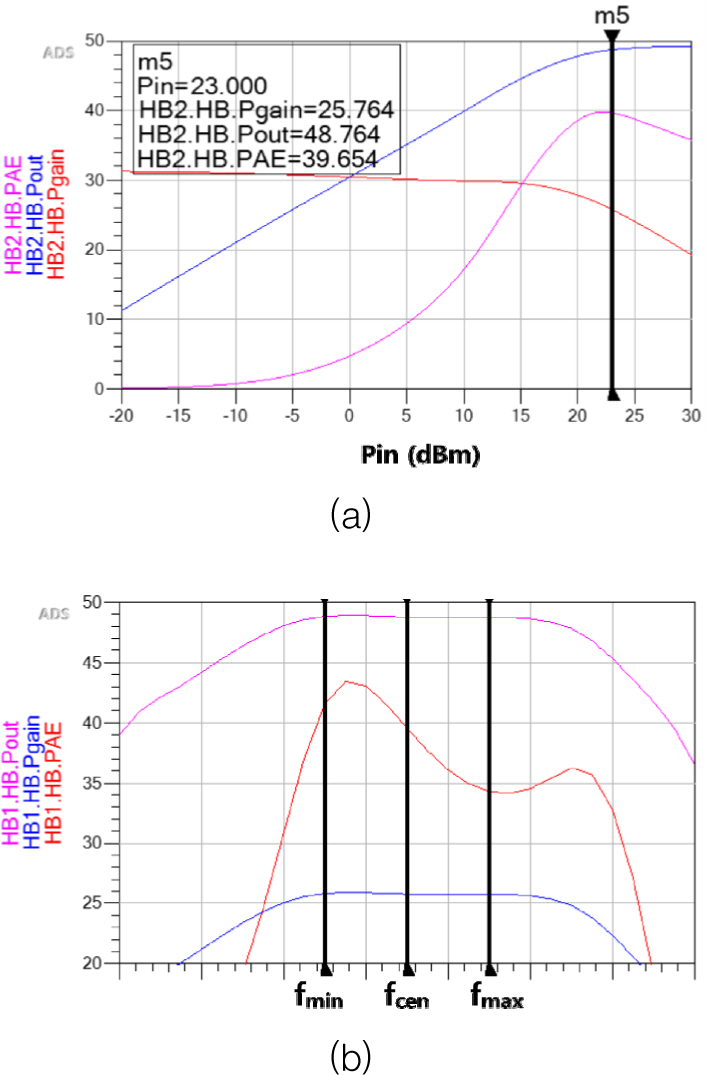

40 W급 고출력 MMIC는 여러 대역폭을 선택하여 사용할 수 있도록 Ku 주파수 대역에서 광대역 특성을 가질 수 있도록 설계하였다. Fig. 2는 설계된 소자의 광대역(Fig. 2 (a)) 그리고 협대역(Fig. 2(b))에서의 s-파라미터 특성을 나타낸 것이다. 드레인 전압 22.5 V와 드레인 전류 740 mA 조건에서 소신호 이득은 대역폭 내에서 30 ∼ 32 dB, 그리고 입력과 출력 반사 손실은 - 20 dB 이하를 나타냄을 확인하였다. 고전력 출력용 MMIC의 최종 출력 특성 확인을 위해서는 대신호 특성 분석이 필요하다. Fig. 3(a)는 입력 전력 증가에 따른 대신호 이득(Pgain: Power gain)과 출력 전력(POUT: Output power) 그리고 전력 부가 효율(PAE: Power Added Efficiency)을 나타낸 것이다. 입력 기준 23 dBm 을 기준으로 대신호 이득은 25.8 dB, 최대 포화 전력은 48.8 dBm 그리고 전력 부가 효율은 39.7 % 를 나타냈다. Fig. 3(b)는 고입력 레벨에서의 주파수 특성을 나타낸 것이다. 고입력 상태에서도 사용 주파수 광대역 내에서 약 48.8 dBm 이상의 출력이 일정하게 발생하는 것을 확인할 수 있었다. 이러한 소신호 그리고 대신호 시뮬레이션 결과를 바탕으로 파운드리 공정 이후에 40 W 이상의 출력을 안정적으로 발생할 수 있을 것으로 예측하였다.

Fig. 4(a)는 Fig. 1의 설계를 바탕으로 UMS사의 파운드리 공정을 통해 제작된 40 W급 MMIC 칩 결과 사진이며, Fig. 4(b)는 제작된 칩을 이용하여 CM1515- 10L 패키지를 적용하여 제작된 모듈 결과이다.

Fig. 5는 듀티 10 % 조건에서 게이트 전압을 20 V, 22.5 V, 24 V, 그리고 27 V 전압을 인가했을 경우의 패키징된 40 W급 고출력 MMIC의 출력 전력(Fig. 5(a))과 전력 부가 효율(Fig. 5(b))의 결과를 나타낸 것이다. 게이트 전압이 증가할수록 출력 전력은 46.7 dBm에서 48.6 dBm까지 증가하였다. 이는 시뮬레이션과 유사한 결과를 보였으며, 패키징 과정에서 손실이 최소화되었음을 나타낸다. 또한, 게이트 전압 변화에 큰 의존성을 보인다. 이는 제작된 칩이 선형 구간에서 동작함을 알 수 있다. 하지만 전력 부가 효율은 시뮬레이션 대비 조금 감소한 값을 보임을 알 수 있다. 이러한 전력 부가 효율의 감소는 몇 가지의 반도체 특성 때문으로 판단된다. 이상적인 전력 부가 효율은 아래의 식 (1)과 (2)와 같다.

하지만, 실제 소자에서는 무릎 전압(knee voltage)이 존재하게 된다. 이럴 경우, 실제 입력되는 DC 전압은 식 (3)과 같이 무릎 전압을 포함한 전압이 인가된다[3,4]. 이러한 DC 전력의 증가는 전력 부가 효율을 낮추는 원인이 된다.

드레인 누설 전류 또한 전력 부가 효율을 낮추는 원인이 된다. 초기 설계 단계에서는 이러한 드레인 누설 전류 현상을 시뮬레이션 단계에 반영하기 힘들다. 하지만 제작된 소자에서는 드레인 누설 전류가 발생하게 되고 이러한 현상은 전력 부가 효율을 낮추는 원인으로 동작하게 된다[5∼7]. 특히 AlGaN/GaN과 같은 이중 접합 구조로 제작되는 HEMT의 경우, 소자 구조적으로 상대적으로 높은 누설 전류를 가지게 된다. 실제 DC 전류는 드레인 전류를 포함하는 식 (4)와 같게 된다.

다른 전력 부가 효율 감소 원인은 소자의 표면과 내부의 전자 포획 현상 따른 DC-to-RF dispersion 현상[8∼10], 고주파수 운용에 의한 게이트-드레인 커패시터와 저항의 변화에 따른 Feedback 현상[11], 그리고 소자의 내부 온도 상승 현상[12,13] 등으로 실제 전력 부가 효율은 감소하게 된다.

3. 70 W급 고출력 모듈 개발

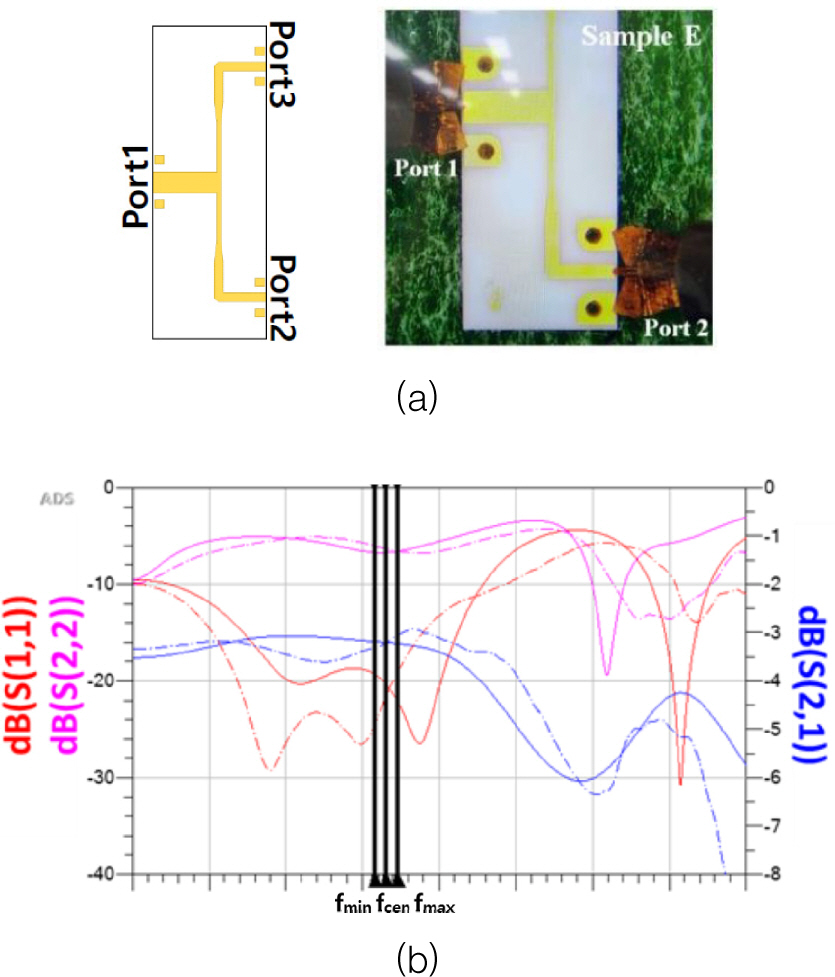

500 W급 송신기를 제작하기 위해서는 70 W급 단위의 모듈을 결합하는 방법으로 구현하였다. 이를 위해서는 40 W급 고출력 MMIC를 패키징 내에서 2-way 결합하는 방법으로 개발을 진행하였다. 결합 방법은 구조가 간단하고 반사 손실 특성을 고려하여 T-junction 결합 방법으로 설계하였다. 그리고 기판은 발열 문제를 최소화하기 위하여 알루미나 기판을 적용하였다. Fig. 6(a)는 T-junction 분배기(결합기)의 설계 이미지와 실제 제작된 T-junction 분배기의 제작 사진이다. Fig. 6(b)은 포트 1과 포트 2 사이의 s-파라미터 특성을 나타낸 것이다. 실선은 시뮬레이션 결과를 그리고 점섬은 측정 결과 나타낸 것이다. 사용 주파수 대역에서 S11의 경우 시뮬레이션에서는 약 - 20 dB 이하의 특성을 보였으며, 측정 결과에서도 약 - 21 dB 이하로 유사한 특성을 보였다. S22의 경우, 시뮬레이션에서 약 - 6.7 dB, 측정에서 - 6.3 dB로 유사한 특성을 보였다. 삽입 손실의 경우, 시뮬레이션과 측정 결과는 0.2와 0.22 dB 수준을 각각 보였다. 이는 시뮬레이션에 제작 과장에 대한 오차 특성이 잘 반영되었기 때문으로 판단된다.

Fabrication of T-junction combiner/divider, (a) design and fabrication, (b) results of simulation and measurement

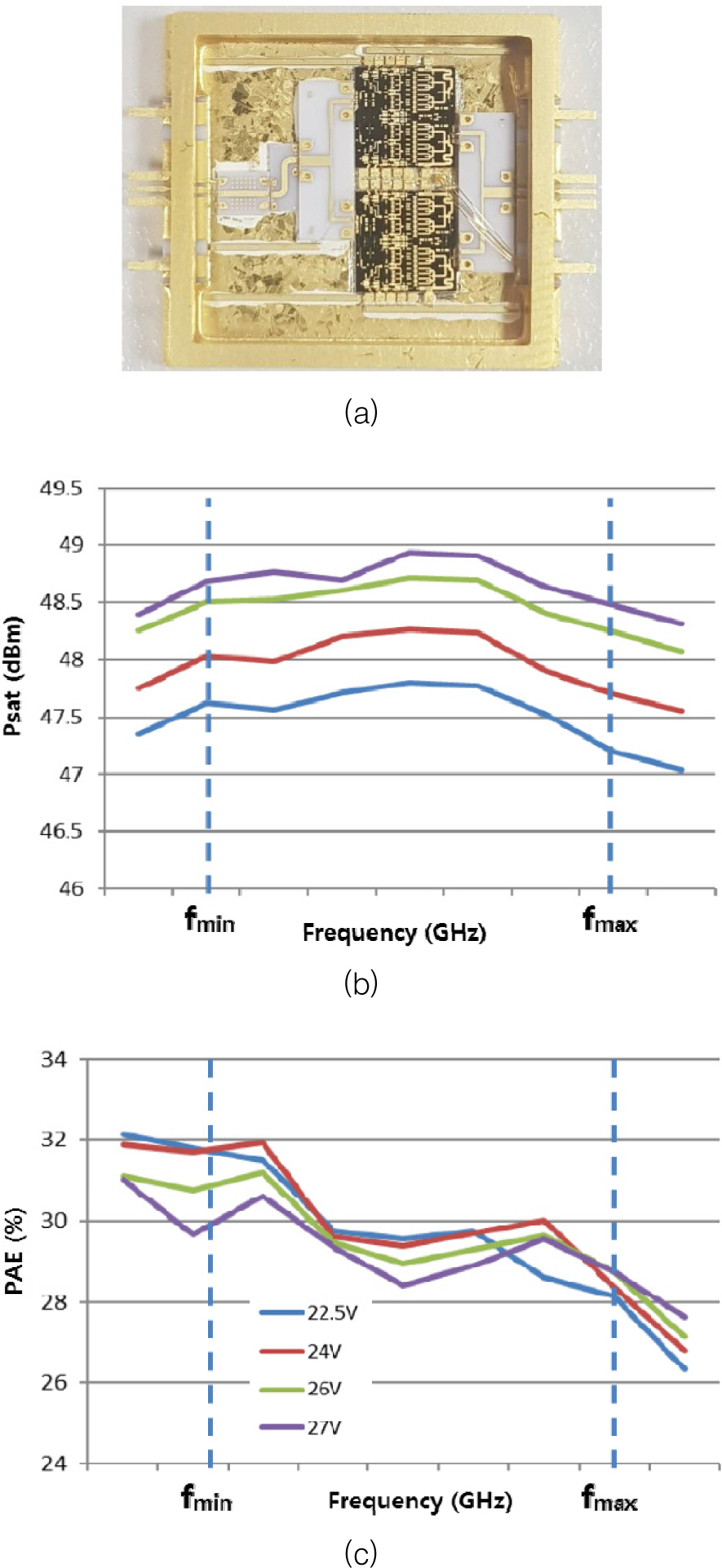

Fig. 7은 40 W급 고출력 MMIC 2개를 T-junction 분배기와 결합기를 이용하여 2-way 방법으로 결합하여 패키징한 70 W급 고출력 증폭기 모듈의 결과 사진과 그 측정 결과를 나타낸 것이다.

Image and measurement results of 70 W-grade GaN power module, (a) module image (b) Output power, (c) Power added efficiency

Fig. 7(a)는 실제 제작된 70 W급 고출력 증폭기 모듈의 사진이다. 입력과 출력단에 T-junction을 적용하였으며, 출력단의 전송선로 손실을 최소화하기 위해 출력단을 패키징 단자와 급전할 수 있도록 배치하였다. 그리고 입력단은 추가적인 전송선로를 추가하여 T-junction과 연결하였다. Fig. 7(b)는 70 W급 고출력 증폭기 모듈의 게이트 전압에 따른 포화 전력 변화를 나타낸 것이다. 게이트 전압을 27 V로 인가하였을 경우, 사용 주파수 대역 모든 주파수 구간에서 70 W를 초과하는 출력을 발생함을 확인하였다. Fig. 7(c)는 게이트 전압 변화에 따른 전력 부가 효율을 나타낸 것이다. 70 W 이상의 출력을 발생하는 주파수 구간 내에서 28 % 이상의 효율을 보임을 확인할 수 있다. 이때 듀티는 10 % 로 실험을 수행하였다.

4. 500W급 SSPA 개발

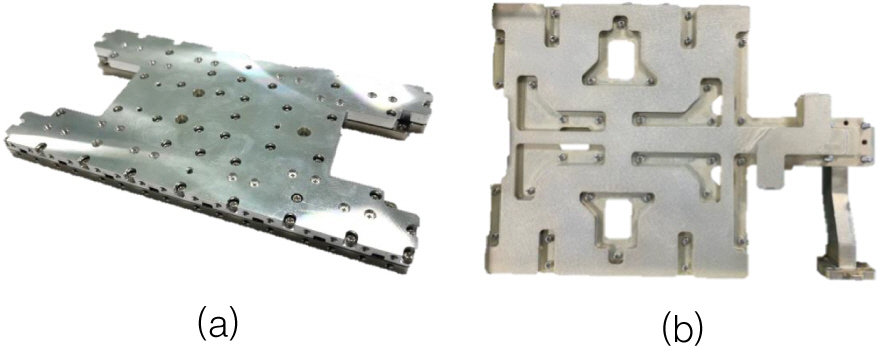

500 W급 반도체형 송신기(SSPA)를 제작하기 위해서는 70 W급 단위의 모듈을 결합하여 전력 증폭기를 구성하였으며, 전력 증폭기 앞 단에 전력 증폭기 입력을 위하여 구동 증폭기를 설계하였다. 전력 증폭기와 구동 증폭기 사이의 전력 분배를 위하여 Fig. 8(a)와 같이 전력 분배기를 제작하였으며, 전력 증폭기의 출력을 결합하기 위해 Fig. 8(b)와 같이 전력 결합기를 제작하여 함께 구성하였다. 전력 분배기와 결합기는 삽입 손실을 최소화하기 위해 도파관 타입으로 개발되었다.

전력 분배기의 경우, 구동 증폭기 출력에서 발생한 신호를 효과적으로 다수의 전력 증폭기에 분배 및 전달하기 위해서, 진폭 변화량(amplitude balance), 위상 변화량(phase balance) 그리고 특히 우수한 격리도(isolation) 특성을 가져야 한다. 반면 전력 결합기의 경우, 다채널 전력 증폭기 출력의 손실을 최소화해서 결합하기 위해서는 우수한 결합 능력(coupling)을 확보해야 한다. Table 2는 20 W급 전력 분배기와 500 W급 전력 결합기의 전기적 특성을 정리한 것이다. 제작 결과 전력 분배기의 격리도 특성은 19 dB 이상을 보였으며, 전력 결합기의 결합 능력은 54.4 ± 0.2 dB 값을 나타내었다. 각각의 삽입 손실은 - 1.5 dB와 - 1 dB의 특성을 보였다.

Fig. 9는 500 W급 반도체형 송신기(SSPA)의 송신 출력 측정 결과이다. 입력 전력 28 V, 입력 준위 3 dBm 그리고 듀비 20 % 의 입력 기준으로 약 504 W의 출력 보임을 확인하였다. 그리고 불요파 특성은 - 58.11 dBc, 위상 변화량은 1.74 °/us, 그리고 출력 잡음 준위는 - 143 dBm/Hz의 특성을 확인하였다. 이러한 반도체형 송신기(SSPA)의 전기적 특성은 기존의 소형 레이더 시스템에서 사용하던 진행파관 증폭기(TWTA)를 대체 가능할 것으로 예상된다.

5. 결 론

본 논문에서는 기존의 진행파관 증폭기를 대체하기 위해 500 W급 반도체형 송신기(SSPA) 개발에 관한 내용을 정리하였다. 반도체형 송신기를 개발하기 위하여, UMS 파운드리를 이용하여 40 W급 고출력 MMIC 를 개발하였으며, 70 W급 전력 모듈 개발을 위하여 T-junction 2-way 결합 방법을 이용하여 모듈을 개발하였다. 이렇게 개발된 전력 모듈을 다채널로 결합하여, 최종 500 W급 반도체형 송신기(SSPA)를 개발하였다.

후 기

이 논문은 2021년 정부(방위사업청)의 재원으로 수행된 연구 결과임.